www.ti.com

PRODUCT PREVIEW

Bit(n-1) (n-2) (n-3)

Bit0 Bit(n-1) (n-2) (n-3)

14

11

10

9

3

3

2

8

6

5

4

4

13

(A)

13

(A)

A. ParameterNo.13appliestothefirstdatabitonly whenXDATDLY ≠0.

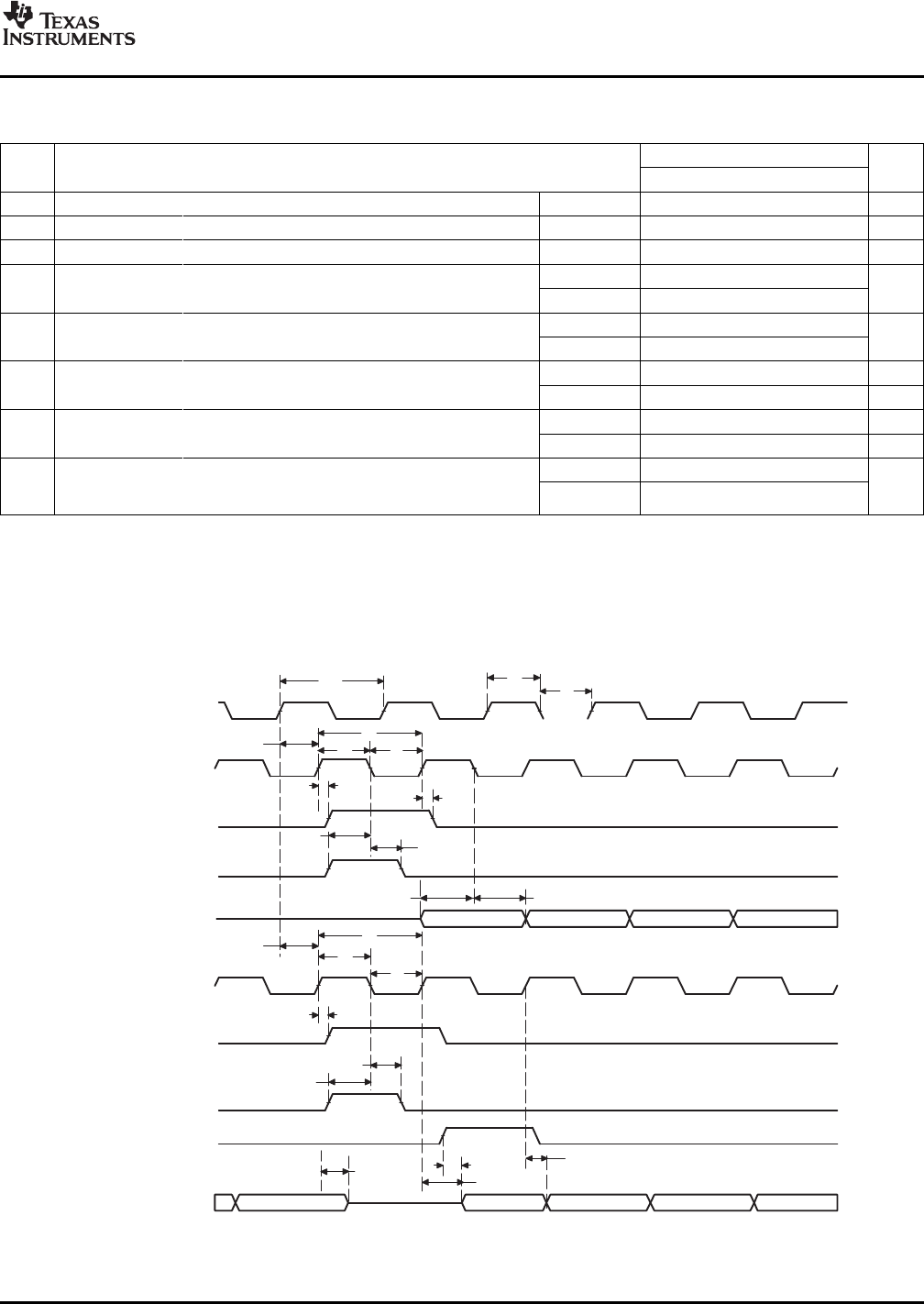

CLKR

FSR(int)

FSR(ext)

DR

CLKX

FSX(int)

FSX(ext)

FSX

(XDATDLY=00b)

DX

15

CLKS

16

16

17

17

3

2

3

7

12

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

Table5-36.SwitchingCharacteristicsOverRecommendedOperatingConditionsforASP

(1)(2)

(seeFigure5-41)

DM355

NO.PARAMETERUNIT

MINMAX

2t

c(CKRX)

Cycletime,CLKR/XCLKR/Xint38.5or2P

(3)(4)

ns

17td(CLKS-CLKRX)Delaytime,CLKShightointernalCLKR/XCLKR/Xint124

3t

w(CKRX)

Pulseduration,CLKR/XhighorCLKR/XlowCLKR/XintC-1C+1ns

CLKRint325

4t

d(CKRH-FRV)

Delaytime,CLKRhightointernalFSRvalidns

CLKRext325

CLKXint-48

9t

d(CKXH-FXV)

Delaytime,CLKXhightointernalFSXvalidns

CLKXext325

CLKXint12ns

tdis(CKXH-Disabletime,DXhighimpedancefollowinglastdata

12

DXHZ)bitfromCLKXhigh

CLKXext12ns

CLKXint-512ns

13t

d(CKXH-DXV)

Delaytime,CLKXhightoDXvalid

CLKXext325ns

Delaytime,FSXhightoDXvalidFSXint14

(5)

14t

d(FXH-DXV)

ONLYapplieswhenindatans

FSXext25

(5)

delay0(XDATDLY=00b)mode

(1)CLKRP=CLKXP=FSRP=FSXP=0.Ifpolarityofanyofthesignalsisinverted,thenthetimingreferencesofthatsignalarealso

inverted.

(2)Minimumdelaytimesalsorepresentminimumoutputholdtimes.

(3)P=(1/SYSCLK2),whereSYSCLK2isanoutputclockofPLLC1(seeSection3.5).

(4)Usewhichevervalueisgreater.

(5)ExtradelayfromFSXhightoDXvalidappliesonlytothefirstdatabitofadevice,ifandonlyifDXENA=1inSPCR.

ifDXENA=0,thenD1=D2=0

ifDXENA=1,thenD1=4P,D2=8P

Figure5-41.ASPTiming

SubmitDocumentationFeedbackPeripheralInformationandElectricalSpecifications139