www.ti.com

PRODUCT PREVIEW

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

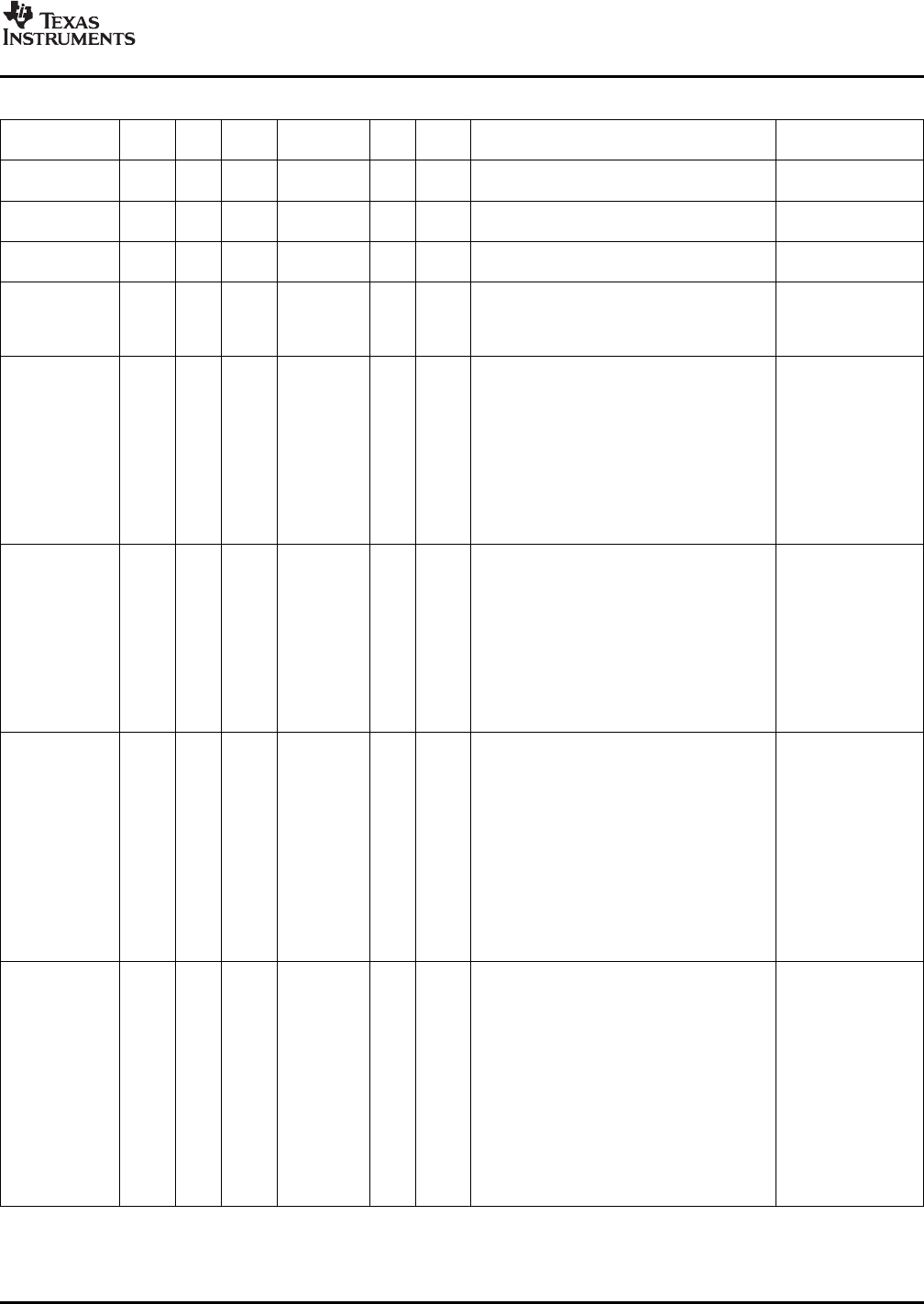

Table2-23.DM355PinDescriptions(continued)

NameBGATypeGroupPowerPUResetDescription

(4)

MuxControl

ID

(1)

Supply

(2)

PD

(3)

State

DDR_VREFU10PWRDDRIV

DD_DDR

DDR:VoltageinputfortheSSTL_18IO

Obuffers

V

SSA_DLL

R11GNDDDRDV

DD_DDR

DDR:GroundfortheDDRDLL

LL

V

DDA33_DDRDLL

R10PWRDDRDV

DD_DDR

DDR:Power(3.3Volts)fortheDDRDLL

LL

DDR_ZNT9I/ODDRIV

DD_DDR

DDR:Referenceoutputfordrivestrength

OcalibrationofNandPchanneloutputs.Tie

togroundvia50ohmresistor@0.5%

tolerance.

EM_A13/V19I/OAEMIV

DD

PDinLAsyncEMIF:AddressBusbit[13]PINMUX2[0].EM_A1

GIO067/F/3_3,

BTSEL[1]GIO/

syste

m

GIO:GIO[067]defaultsetby

AECFG[0]

System:BTSEL[1:0]sampledat

Power-on-ResettodetermineBootmethod

(00:NAND,01:Flash,10:UART,11:SD)

EM_A12/U19I/OAEMIV

DD

PDinLAsyncEMIF:AddressBusbit[12]PINMUX2[0].EM_A1

GIO066/F/3_3,

BTSEL[0]GIO/

syste

m

GIO:GIO[066]defaultsetby

AECFG[0]

System:BTSEL[1:0]sampledat

Power-on-ResettodetermineBootmethod

(00:NAND,01:Flash,10:UART,11:SD)

EM_A11/R16I/OAEMIV

DD

PUinHAsyncEMIF:AddressBusbit[11]PINMUX2[0].EM_A1

GIO065/F/3_3,

AECFG[3]GIO/

syste

m

GIO:GIO[065]defaultsetby

AECFG[0]

System:AECFG[3:0]sampledat

Power-on-ResettosetAEMIFConfiguration

AECFG[3]setsdefaultfor

PinMux2.EM_D15_8:AEMIFDefaultBus

Width(0:16or1:8bits)

EM_A10/R18I/OAEMIV

DD

PUinHAsyncEMIF:AddressBusbit[10]PINMUX2[0].EM_A1

GIO064/F/3_3,

AECFG[2]GIO/

syste

m

GIO:GIO[064]defaultsetby

AECFG[0]

System:AECFG[3:0]sampledat

Power-on-ResettosetAEMIFConfiguration

AECFG[2:1]setsdefaultfor

PinMux2.EM_BA0:AEMIFEM_BA0

Definition(00:EM_BA0,01:EM_A14,

10:GIO[054],11:rsvd)

SubmitDocumentationFeedbackDeviceOverview43