www.ti.com

PRODUCT PREVIEW

5.2RecommendedClockandControlSignalTransitionBehavior

5.3PowerSupplies

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

AllclocksandcontrolsignalsshouldtransitionbetweenV

IH

andV

IL

(orbetweenV

IL

andV

IH

)ina

monotonicmanner.

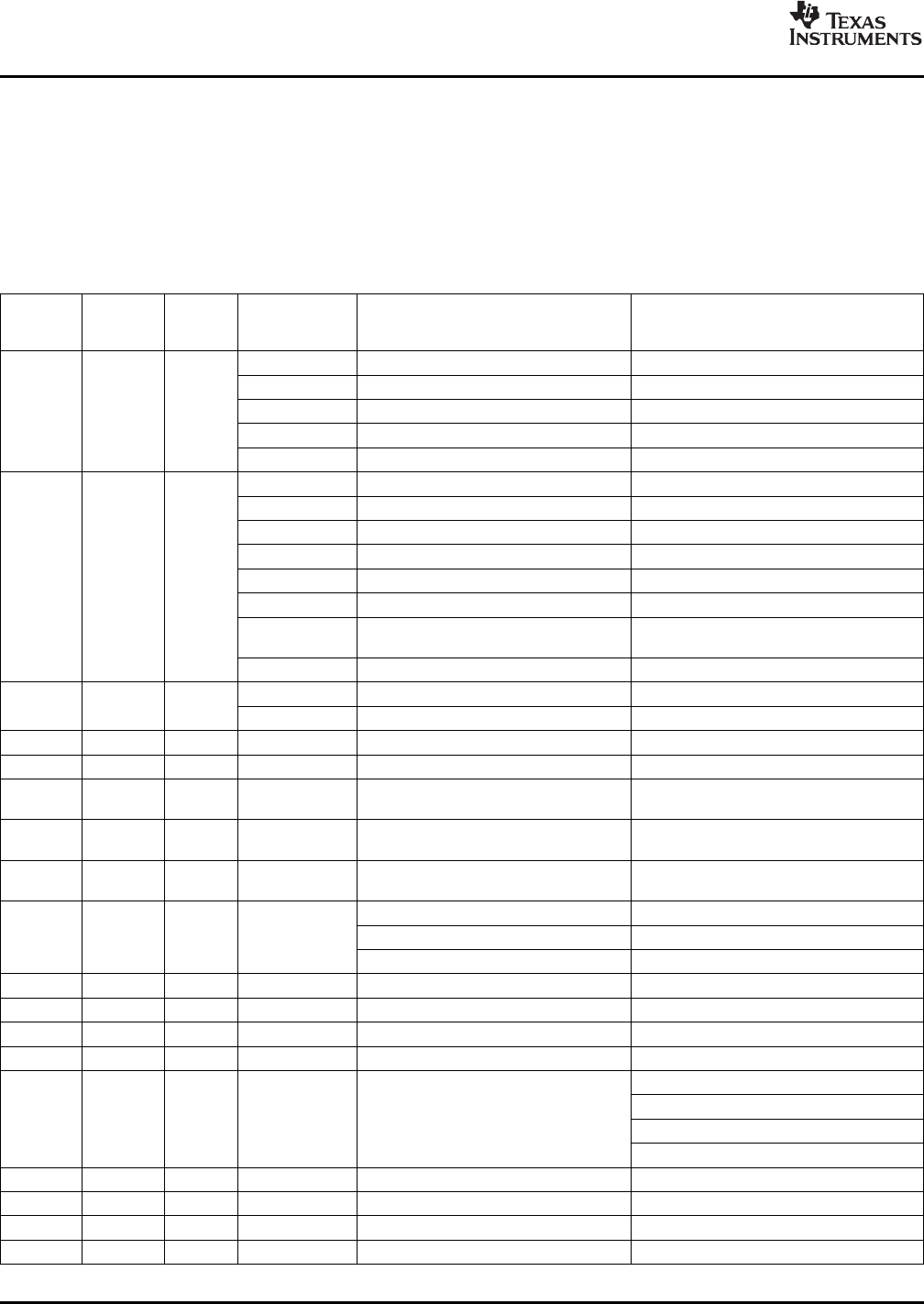

ThepowersuppliesofDM355aresummarizedinTable5-1.

Table5-1.PowerSupplies

CustomerTolerancePackageChipPlaneDescriptionComments

BoardPlaneName

Supply

1.3V±5%1.3VCV

DD

CoreV

DD

V

DDA_PLL1

PLL1V

DDA

V

DDA_PLL2

PLL2V

DDA

V

DDD13_USB

USB1.3Vsupply

V

DDA13_USB

USB1.3Vsupply

3.3V±5%3.3VV

DD

IOV

DD

forLVCMOSV

DDSHV

V

DD

IOV

DD

forMXI/O1V

DDSHV

V

DD

IOV

DD

forMXI/O2V

DDSHV1

V

DD

IOV

DD

forISBDRVVBUSV

DDSHV2

V

DDA33_DDRDLL

DDRDLLanalogV

DD

V

DDA33_USB

Analog3.3VpowerUSBPHY

V

DDA33_USB_PLL

Commonmode3.3VpowerforUSB

PHY(PLL)

V

DD

IOV

DD

forperipherals

3.3V±5%3.3VV

DD_VIN

IOV

DD

forVideoINI/F

V

DD_VOUT

IOV

DD

forVideoOUTI/F

1.8V±5%1.8VV

DD_DDR

1.8V±5%1.8VV

DDA18

Analog1.8Vpower

1.8V±5%1.8VV

DDA18_DAC

Placedecouplingcaps(0.1μF/10μf)close

tochip

0Vn/a0VV

SS_MX1

Connecttoexternalcrystalcapacitor

ground

0Vn/a0VV

SS_MX2

Connecttoexternalcrystalcapacitor

ground

0Vn/a0VV

SS

Chipground

USBESDground

groundV

SS

0Vn/a0VV

SSA

groundKeepseparatefromdigitalgroundV

SS

0Vn/a0VV

SA_PLL1

PLL1V

SSA

0Vn/a0VV

SSA_PLL2

PLL2V

SSA

0Vn/a0VV

SSA_DLL

DLLground

0Vn/a0VV

SS_USB

USBgroundV

SSA13_USB

V

SSA13_USB

V

SSA33_USB

V

SSA33_USB_PLL

0Vn/a0VV

SS_USB_REF

USBPHYreferencegroundV

SSREF

0Vn/a0VV

SSA_DAC

DACgroundKeepseparatefromdigitalgroundV

SS

V

DDS

*0.5V

DDS

*0.5V

REFSSTL

DRRrefvoltageV

DDS

dividedby2,throughboardresistors

5V5VUSB_VBUSVBUSConnecttoexternalchargepump

PeripheralInformationandElectricalSpecifications 96SubmitDocumentationFeedback