www.ti.com

PRODUCT PREVIEW

3.5DeviceClocking

3.5.1Overview

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

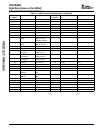

TheDM355requiresoneprimaryreferenceclock.Thereferenceclockfrequencymaybegenerated

eitherbycrystalinputorbyexternaloscillator.Thereferenceclockistheclockatthepinsnamed

MXI1/MXOI.ThereferenceclockdrivestwoseparatePLLcontrollers(PLLC1andPLLC2).PLLC1

generatestheclocksrequiredbytheARM,MPEGandJPEGco-processor,VPBE,VPSS,and

peripherals.PLL2generatestheclockrequiredbytheDDRPHY.AblockdiagramofDM355'sclocking

architectureisshowninFigure5-1.ThePLLsaredescribedfurtherinSection3.6.

SubmitDocumentationFeedbackDetailedDeviceDescription65