www.ti.com

PRODUCT PREVIEW

3.9.2SoftwareControlledPinMultiplexing

3.10DeviceReset

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

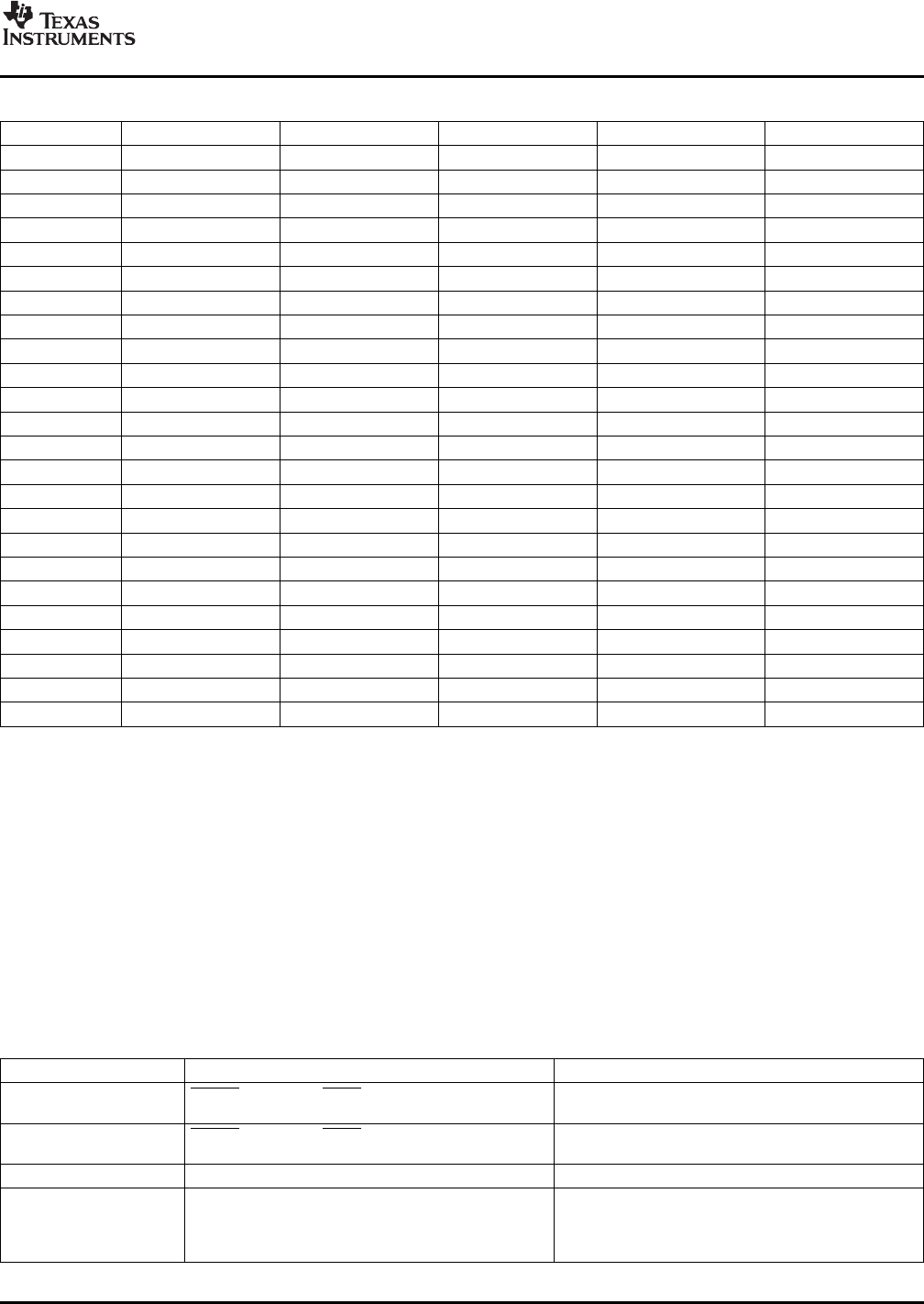

Table3-13.AECFG(AsyncEMIFConfiguration)PinMuxCoding

1101(NAND)11001010(OneNAND)1000(8-bitSRAM)0010(16-bitSRAM)0000

GPIO[54]GPIO[54]EM_A[14]EM_BA[0]EM_A[14]EM_BA[0]

GPIO[55]EM_BA[1]EM_BA[1]EM_BA[1]EM_BA[1]EM_BA[1]

GPIO[56]EM_A[0]EM_A[0]EM_A[0]EM_A[0]EM_A[0]

EM_A[1]EM_A[1]EM_A[1]EM_A[1]EM_A[1]EM_A[1]

EM_A[2]EM_A[2]EM_A[2]EM_A[2]EM_A[2]EM_A[2]

GPIO[57]EM_A[3]EM_A[3]EM_A[3]EM_A[3]EM_A[3]

GPIO[58]EM_A[4]EM_A[4]EM_A[4]EM_A[4]EM_A[4]

GPIO[59]EM_A[5]EM_A[5]EM_A[5]EM_A[5]EM_A[5]

GPIO[60]EM_A[6]EM_A[6]EM_A[6]EM_A[6]EM_A[6]

GPIO[61]EM_A[7]EM_A[7]EM_A[7]EM_A[7]EM_A[7]

GPIO[62]EM_A[8]EM_A[8]EM_A[8]EM_A[8]EM_A[8]

GPIO[63]EM_A[9]EM_A[9]EM_A[9]EM_A[9]EM_A[9]

GPIO[64]EM_A[10]EM_A[10]EM_A[10]EM_A[10]EM_A[10]

GPIO[65]EM_A[11]EM_A[11]EM_A[11]EM_A[11]EM_A[11]

GPIO[66]EM_A[12]EM_A[12]EM_A[12]EM_A[12]EM_A[12]

GPIO[67]EM_A[13]EM_A[13]EM_A[13]EM_A[13]EM_A[13]

GPIO[46]GPIO[46]GPIO[46]GPIO[46]EM_D[8]EM_D[8]

GPIO[47]GPIO[47]GPIO[47]GPIO[47]EM_D[9]EM_D[9]

GPIO[48]GPIO[48]GPIO[48]GPIO[48]EM_D[10]EM_D[10]

GPIO[49]GPIO[49]GPIO[49]GPIO[49]EM_D[11]EM_D[11]

GPIO[50]GPIO[50]GPIO[50]GPIO[50]EM_D[12]EM_D[12]

GPIO[51]GPIO[51]GPIO[51]GPIO[51]EM_D[13]EM_D[13]

GPIO[52]GPIO[52]GPIO[52]GPIO[52]EM_D[14]EM_D[14]

GPIO[53]GPIO[53]GPIO[53]GPIO[53]EM_D[15]EM_D[15]

AllpinmultiplexingoptionsareconfigurablebysoftwareviapinmuxregistersthatresideintheSystem

ControlModule.ThePinMux0RegistercontrolstheVideoInmuxing,PinMux1registercontrolsVideoOut

signals,PinMux2registercontrolsAEMIFsignals,PinMux3registerscontrolthemultiplexingoftheGIO

signals,thePinMux4registercontrolstheSPIandMMC/SD0signals.RefertotheARMSubsystemUser's

Guideforcompletedescriptionsofthepinmuxregisters.

TherearefivetypesofresetinDM355.Thetypesofresetdifferbyhowtheyareinitiatedand/orbytheir

effectonthechip.EachtypeisbrieflydescribedinTable3-14andfurtherdescribedintheARM

SubsystemGuide.

Table3-14.ResetTypes

TypeInitiatorEffect

POR(Power-On-Reset)RESETpinlowandTRSTlowTotalresetofthechip(coldreset).Resetsallmodules

includingmemoryandemulation.

WarmResetRESETpinlowandTRSThigh(initiatedbyARMResetsallmodulesincludingmemory,exceptARM

emulator).emulation.

MaxResetARMemulatororWatchdogTimer(WDT).Sameeffectaswarmreset.

SystemResetARMemulatorResetsallmodulesexceptmemoryandARM

emulation.Itisasoftresetthatmaintainsmemory

contentsanddoesnotaffectorresetclocksorpower

states.

SubmitDocumentationFeedbackDetailedDeviceDescription79