www.ti.com

PRODUCT PREVIEW

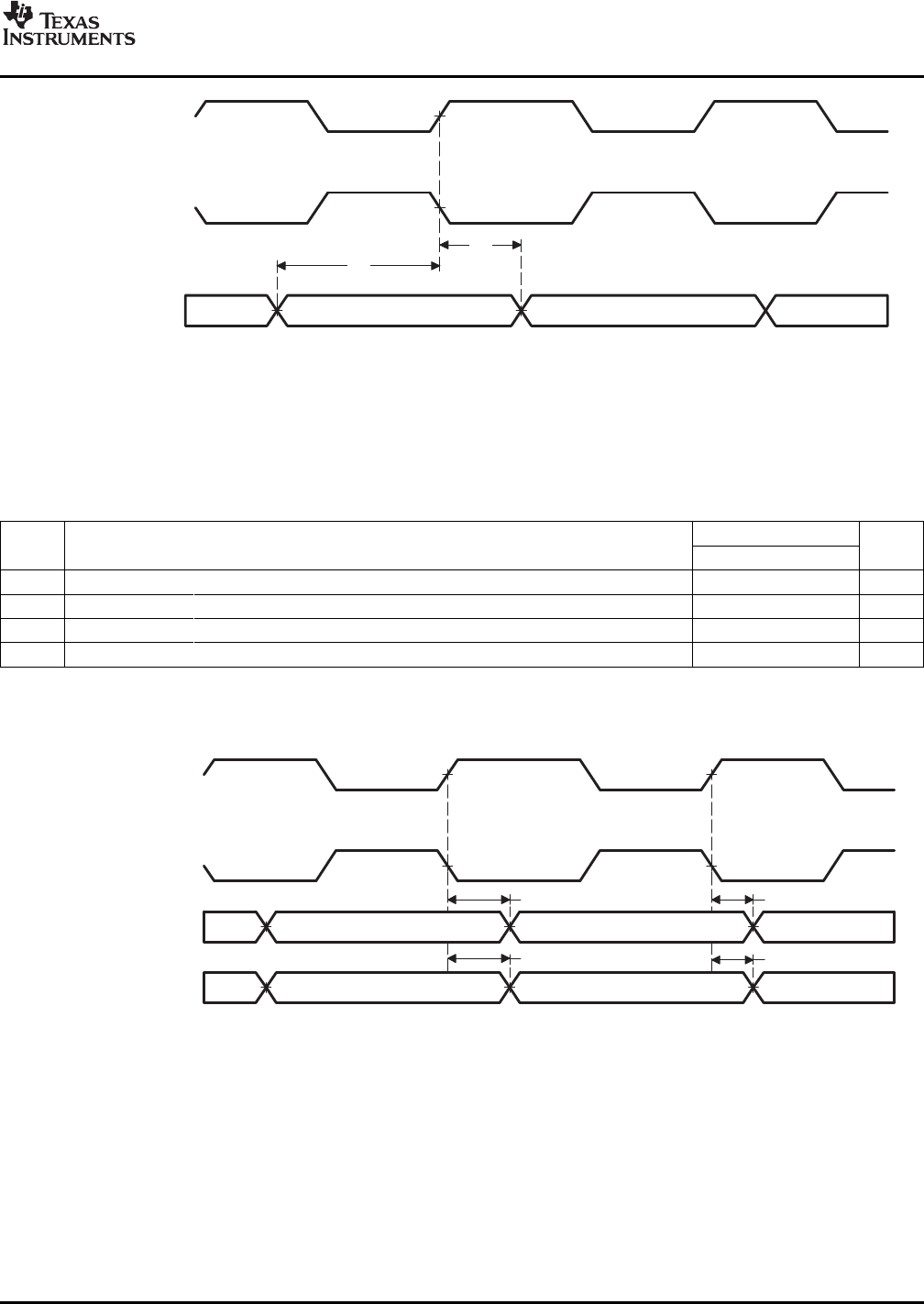

VCLKIN

(A)

(Positive Edge Clocking)

9

VCLKIN

(A)

(Negative Edge Clocking)

10

VCTL

(B)

A. VCLKIN=PCLKorEXTCLK

B. VCTL=HSYNC,VSYNC,andFIELD

VCLKIN

(A)

(Positive Edge Clocking)

13

VCLKIN

(A)

(Negative Edge Clocking)

11

VCTL

(B)

A. VCLKIN=PCLKorEXTCLK

B. VCTL=HSYNC,VSYNC,FIELD,andLCD_OE

C. VDATA=COUT[7:0],YOUT[7:0],R[7:3],G[7:2],andB[7:3]

VDATA

(C)

14

12

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

Figure5-28.VPBEInputTimingWithRespecttoPCLKandEXTCLK

Table5-23.SwitchingCharacteristicsOverRecommendedOperatingConditionsforVPBEControland

DataOutputWithRespecttoPCLKandEXTCLK

(1)(2)(3)

(seeFigure5-29)

DM355

NO.PARAMETERUNIT

MINMAX

11t

d(VCLKIN-VCTLV)

Delaytime,VCLKINedgetoVCTLvalid13.3ns

12t

d(VCLKIN-VCTLIV)

Delaytime,VCLKINedgetoVCTLinvalid2ns

13t

d(VCLKIN-VDATAV)

Delaytime,VCLKINedgetoVDATAvalid13.3ns

14t

d(VCLKIN-VDATAIV)

Delaytime,VCLKINedgetoVDATAinvalid2ns

(1)TheVPBEmaybeconfiguredtooperateineitherpositiveornegativeedgeclockingmode.Wheninpositiveedgeclockingmode,the

risingedgeofVCLKINisreferenced.Wheninnegativeedgeclockingmode,thefallingedgeofVCLKINisreferenced.

(2)VCLKIN=PCLKorEXTCLK

(3)VCTL=HSYNC,VSYNC,FIELD,andLCD_OE

Figure5-29.VPBEControlandDataOutputWithRespecttoPCLKandEXTCLK

SubmitDocumentationFeedbackPeripheralInformationandElectricalSpecifications123