www.ti.com

PRODUCT PREVIEW

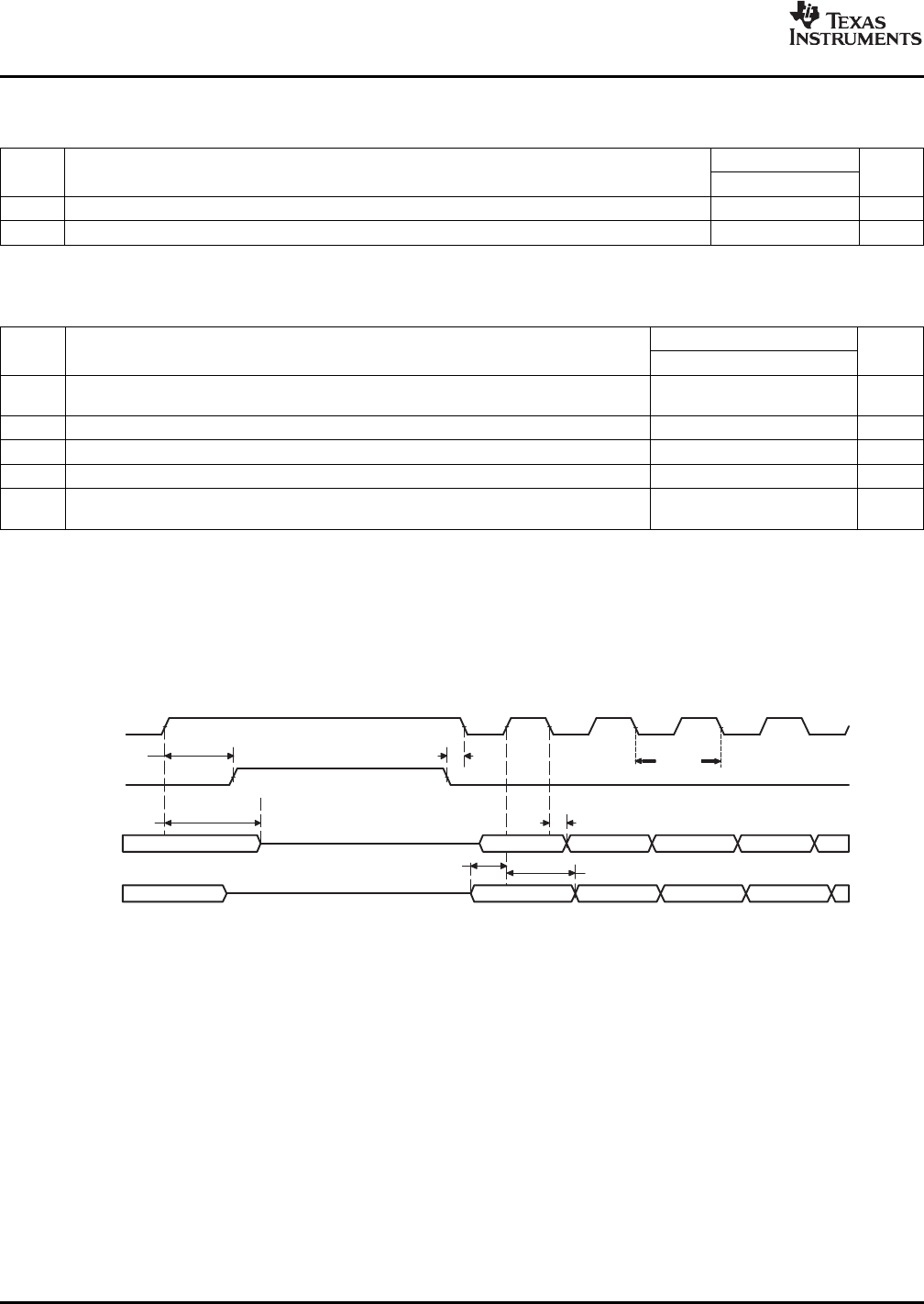

Bit0 Bit(n-1) (n-2) (n-3) (n-4)

Bit0 Bit(n-1) (n-2) (n-3) (n-4)

M50

M49

M45

M46

M44

M43

CLKX

FSX

DX

DR

M52

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

Table5-41.ASPasSPITimingRequirements

CLKSTP=10b,CLKXP=1(seeFigure5-44)

MASTER

NO.UNIT

MINMAX

M49t

su(DRV-CKXH)

Setuptime,DRvalidbeforeCLKXhigh11ns

M50t

h(CKXH-DRV)

Holdtime,DRvalidafterCLKXhigh0ns

Table5-42.ASPasSPISwitchingCharacteristics

(1)(2)

CLKSTP=10b,CLKXP=1(seeFigure5-44)

MASTER

NO.PARAMETERUNIT

MINMAX

38.5or

M52tc(CKX)Cycletime,CLKXns

2P

(1)(3)

M43t

d(CKXH-FXH)

Delaytime,CLKXhightoFSXhigh

(4)

T–1T+3ns

M44t

d(FXL-CKXL)

Delaytime,FSXlowtoCLKXlow

(5)

D–2D+2ns

M45t

d(CKXL-DXV)

Delaytime,CLKXlowtoDXvalid–26ns

Disabletime,DXhighimpedancefollowinglastdatabitfrom

M46t

dis(CKXH-DXHZ)

D–3D+3ns

CLKXhigh

(1)P=(1/SYSCLK2),whereSYSCLK2isanoutputclockofPLLC1(seeSection3.5).

(2)T=CLKXperiod=(1+CLKGDV)×P

C=CLKXlowpulsewidth=T/2whenCLKGDVisoddorzeroand=(CLKGDV/2)×PwhenCLKGDViseven

D=CLKXhighpulsewidth=T/2whenCLKGDVisoddorzeroand=(CLKGDV/2+1)×PwhenCLKGDViseven

(3)Usewhichevervalueisgreater.

(4)FSRP=FSXP=1.AsaSPImaster,FSXisinvertedtoprovideactive-lowslave-enableoutput.

CLKXM=FSXM=1,CLKRM=FSRM=0formasterASP

(5)FSXshouldbelowbeforetherisingedgeofclocktoenableslavedevicesandthenbeginaSPItransferattherisingedgeofthemaster

clock(CLKX).

Figure5-44.ASPasSPI:CLKSTP=10b,CLKXP=1

142PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback