www.ti.com

PRODUCT PREVIEW

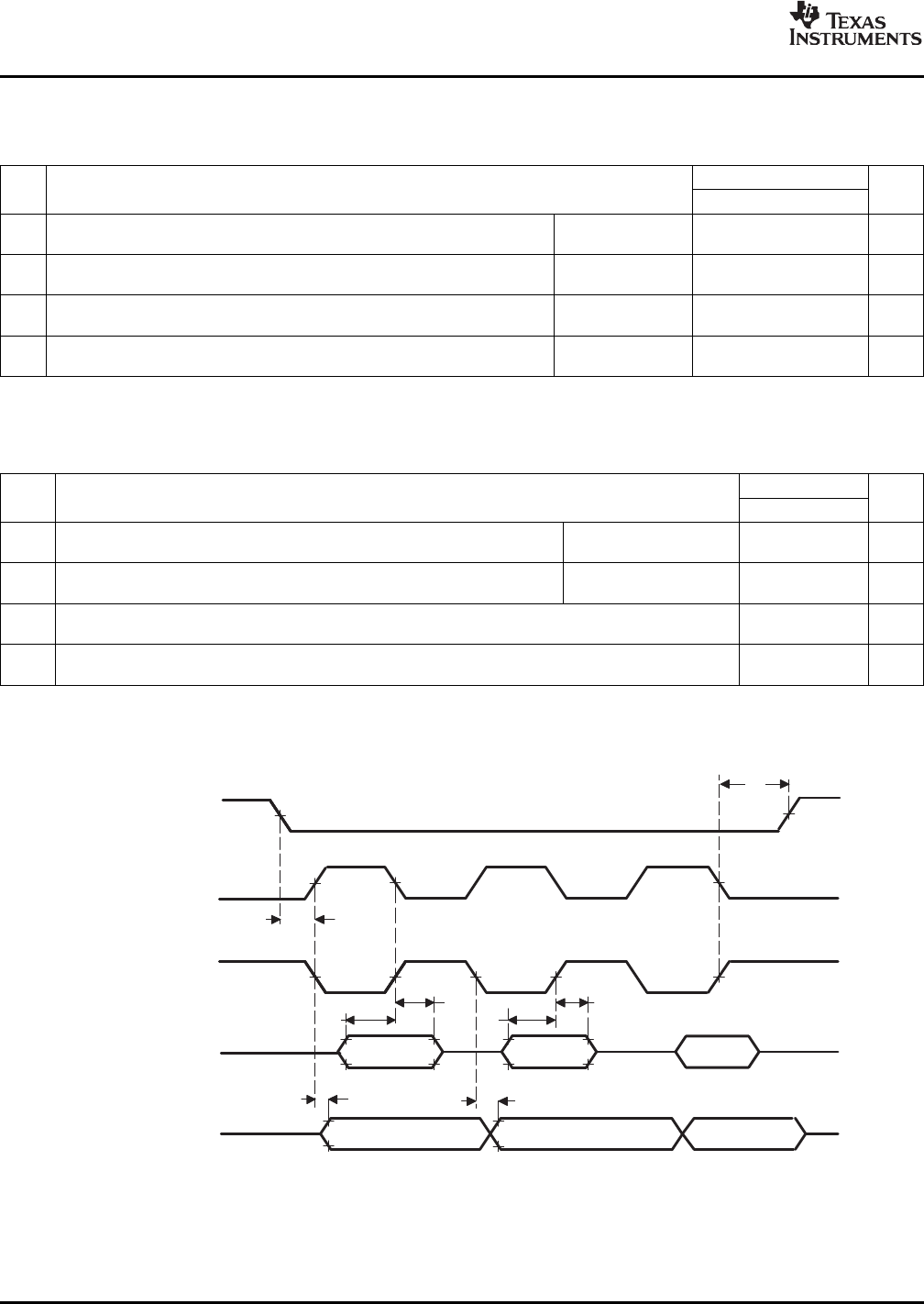

SPI_CLK

(ClockPolarity=0)

SPI_CLK

(ClockPolarity=1)

SPI_DI

(Input)

SPI_DO

(Output)

4

MSBIN DATA LSBIN

LSBOUTMSBOUT DATA

9

10

8

6

5

7

SPI_EN

11

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

SPIMasterModeTimings(ClockPhase=0)

Table5-29.TimingRequirementsforSPIMasterMode[ClockPhase=0]

(1)

(seeFigure5-37)

DM355

NO.UNIT

MINMAX

Setuptime,SPI_DI(input)validbeforeSPI_CLK(output)

4t

su(DIV-CLKL)

ClockPolarity=0.5P+3ns

fallingedge

Setuptime,SPI_DI(input)validbeforeSPI_CLK(output)

5t

su(DIV-CLKH)

ClockPolarity=1.5P+3ns

risingedge

Holdtime,SPI_DI(input)validafterSPI_CLK(output)falling

6t

h(CLKL-DIV)

ClockPolarity=0.5P+3ns

edge

Holdtime,SPI_DI(input)validafterSPI_CLK(output)rising

7t

h(CLKH-DIV)

ClockPolarity=12.5P+3ns

edge

(1)P=PeriodoftheSPImoduleclockinnanoseconds(P=PLL1/6).

Table5-30.SwitchingCharacteristicsOverRecommendedOperatingConditionsforSPIMasterMode

[ClockPhase=0](seeFigure5-37)

DM355

NO.PARAMETERUNIT

MINMAX

Delaytime,SPI_CLK(output)risingedgetoSPI_DO

8t

d(CLKH-DOV)

ClockPolarity=0-45ns

(output)transition

Delaytime,SPI_CLK(output)fallingedgetoSPI_DO

9t

d(CLKL-DOV)

ClockPolarity=1-45ns

(output)transition

Delaytime,SPI_EN[1:0](output)fallingedgetofirstSPI_CLK(output)risingorfalling

10t

d(ENL-CLKH/L)

2P

(1)(1)

ns

edge

P+.5C

(2

11t

d(CLKH/L-ENH)

Delaytime,SPI_CLK(output)risingorfallingedgetoSPI_EN[1:0](output)risingedge

(2)

ns

)

(1)ThedelaytimecanbeadjustedusingtheSPImoduleregisterC2TDELAY.SeetheTMS320DM355DMSoCSerialPeripheralInterface

(SPI)User'sGuide(SPRUED4).

(2)ThedelaytimecanbeadjustedusingtheSPImoduleregisterT2CDELAY.SeetheTMS320DM355DMSoCSerialPeripheralInterface

(SPI)User'sGuide(SPRUED4).

Figure5-37.SPIMasterModeExternalTiming(ClockPhase=0)

PeripheralInformationandElectricalSpecifications 132SubmitDocumentationFeedback