www.ti.com

PRODUCT PREVIEW

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

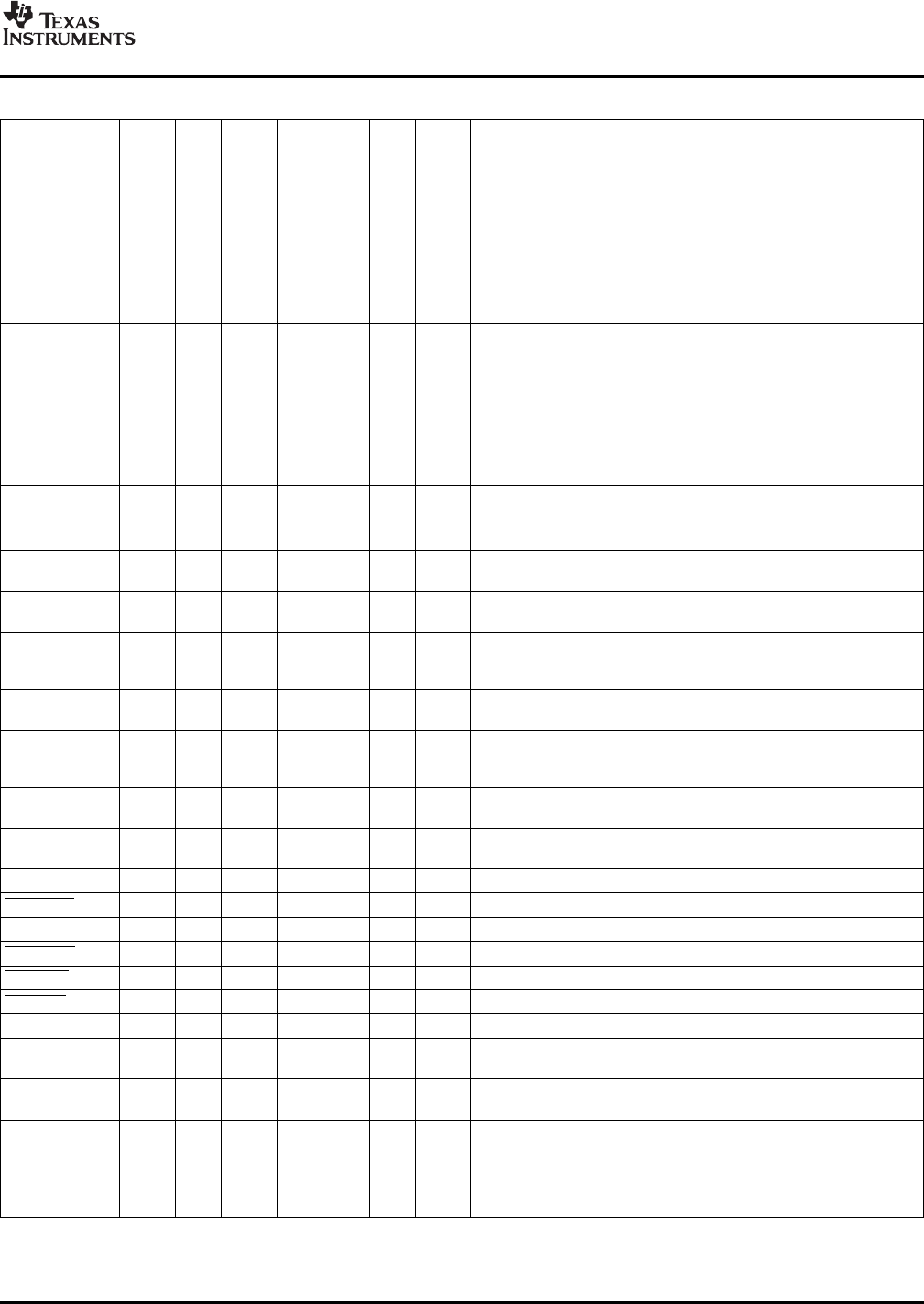

Table2-23.DM355PinDescriptions(continued)

NameBGATypeGroupPowerPUResetDescription

(4)

MuxControl

ID

(1)

Supply

(2)

PD

(3)

State

FIELD/GIO070H4I/OVENCV

DD_VOUT

inVideoEncoder:FieldidentifierforinterlacedPINMUX1[19:18].FI

/R2/PWM3C/GIO/displayformatsELD

VENC

/

PWM3

GIO:GIO[070]

DigitalVideoOut:R2

PWM3C

(4)

EXTCLK/G3I/OVENCV

DD_VOUT

PDinVideoEncoder:Externalclockinput,usedifPINMUX1[21:20].EX

GIO069/B2//GIO/clockrates>27MHzareneeded,e.g.74.25TCLK

PWM3DVENCMHzforHDTVdigitaloutput

/

PWM3

GIO:GIO[069]

DigitalVideoOut:B2

PWM3D

(4)

VCLK/GIO068H3I/OVENCV

DD_VOUT

outLVideoEncoder:VideoOutputClockPINMUX1[22].VCLK

/GIO

GIO:GIO[068]

(4)

VREFJ7AI/OVideoVideoDAC:Referencevoltageoutput

DAC(0.45V,0.1uFtoGND)

IOUTE1AI/OVideoVideoDAC:PrevideobufferDACoutput

DAC(1000ohmtoVFB)

IBIASF2AI/OVideoVideoDAC:Externalresistor(2550Ohmsto

DACGND)connectionforcurrentbias

configuration

VFBG1AI/OVideoVideoDAC:PrevideobufferDACoutput

DAC(1000ohmtoIOUT,1070ohmtoTVOUT)

TVOUTF1AI/OVideoV

DDA18_DAC

VideoDAC:AnalogCompositeNTSC/PAL

DACoutput(SeeFigure5-31andFigure5-32for

circuitconnection)

V

DDA18V_DAC

L7PWRVideoVideoDAC:Analog1.8Vpower

DAC

V

SSA_DAC

L8GNDVideoVideoDAC:Analog1.8Vground

DAC

DDR_CLKW9I/ODDRV

DD_DDR

outLDDRDataClock

DDR_CLKW8I/ODDRV

DD_DDR

outHDDRComplementaryDataClock

DDR_RAST6I/ODDRV

DD_DDR

outHDDRRowAddressStrobe

DDR_CASV9I/ODDRV

DD_DDR

outHDDRColumnAddressStrobe

DDR_WEW10I/ODDRV

DD_DDR

outHDDRWriteEnable(activelow)

DDR_CST8I/ODDRV

DD_DDR

outHDDRChipSelect(activelow)

DDR_CKEV10I/ODDRV

DD_DDR

outLDDRClockEnable

DDR_DQM[1]U15I/ODDRV

DD_DDR

outLDatamaskoutputs:DQM0:For

DDR_DQ[7:0]

DDR_DQM[0]T12I/ODDRV

DD_DDR

outLDatamaskoutputs:DQM1:For

DDR_DQ[15:8]

DDR_DQS[1]V15I/ODDRV

DD_DDR

inDatastrobeinput/outputsforeachbyteof

the16bitdatabususedtosynchronizethe

datatransfers.OutputtoDDRwhenwriting

andinputswhenreading.

DQS1:ForDDR_DQ[15:8]

SubmitDocumentationFeedbackDeviceOverview41