www.ti.com

PRODUCT PREVIEW

3.5.4PeripheralClockingConsiderations

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

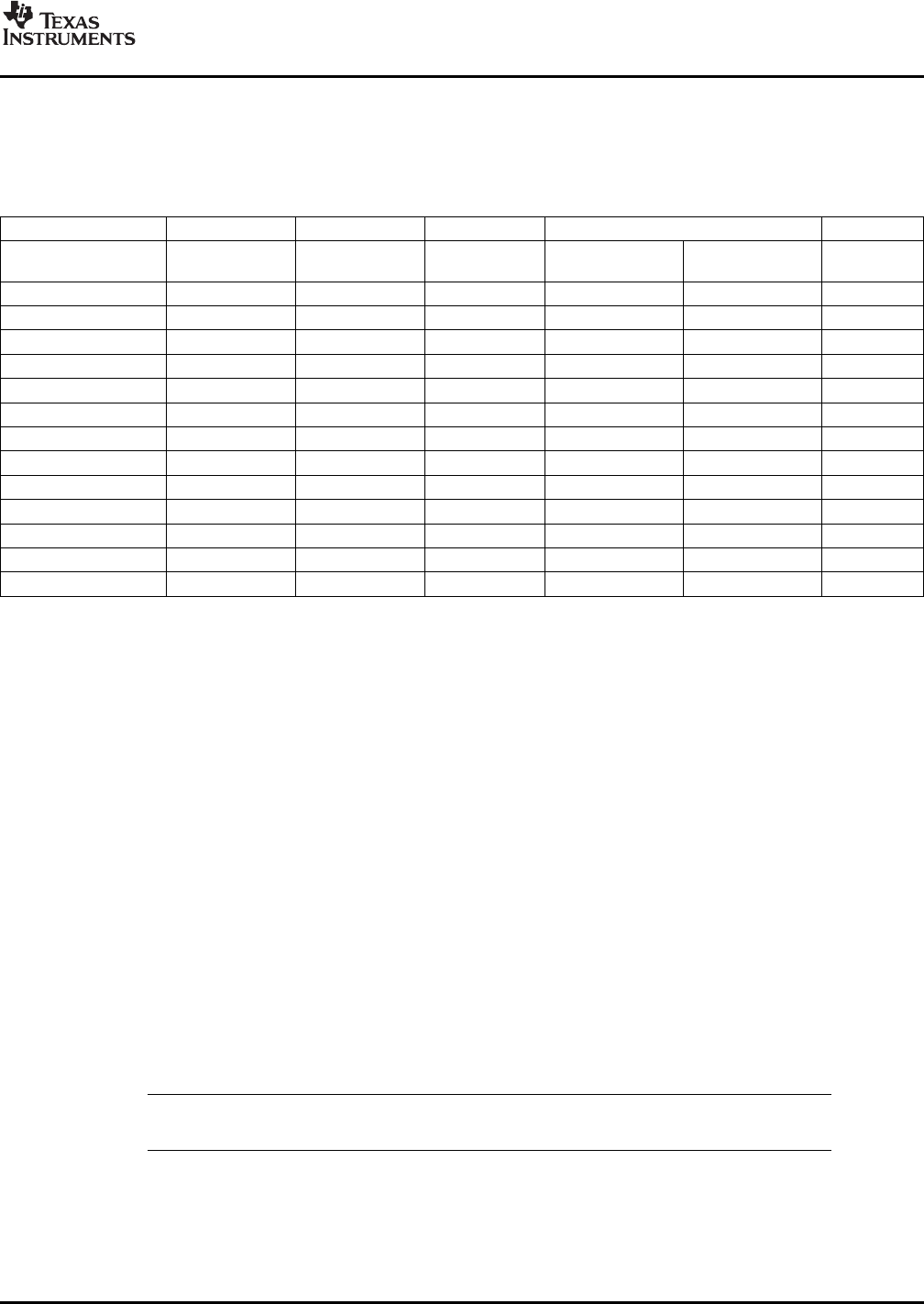

3.5.3.2.2DM355-270PLL2(36MHzreference)

AllsupportedclockingconfigurationsforDM355-270PLL2with36MHzreferenceclockareshownin

Table3-5

Table3-9.PLL2SupportedClockingConfigurationsforDM355-270(36MHzreference)

PREDIVPLLMPOSTDIVPLL2VCODDRPHYDDRClock

(/nprogrammable)(m(/1fixed)(MHz)PLLDIV1SYSCLK1DDR_CLK

programmable)(/1fixed)(MHz)(MHz)

bypassbypassbypassbypass13618

1214414321432216

1213814141414207

1213213961396198

1212613781378189

1212013601360180

1211413421342171

1210813241324162

1210213061306153

129612881288144

1813312661266133

2715012001200100

271201160116080

3.5.4.1VideoProcessingBackEndClocking

TheVideoProcessingBackEnd(VPBE)isasub-moduleoftheVPSS(VideoProcessingSubsystem).

TheVPBEisdesignedtointerfacewithavarietyofLCDsandaninternalDACmodule.Therearetwo

asynchronousclockdomainsintheVPBE:aninternalclockdomainandanexternalclockdomain.The

internalclockdomainisdrivenbytheVPSSclock(PLL1SYSCLK4).Theexternalclockdomainis

configurable;youcanselectoneoffivesource:

•24MHzcrystalinputatMXI1

•27MHzcrystalinputatMXI2(optionalfeature,nottypicallyused)

•PLL1SYSCLK3

•EXTCLKpin(externalVPBEclockinputpin)

•PCLKpin(VPFEpixelclockinputpin)

SeetheTMS320DM355DMSoCVideoProcessingBackEnd(VPBE)User'sGuideforcomplete

informationonVPBEclocking.

3.5.4.2USBClocking

TheUSBControllerisdrivenbytwoclocks:anoutputclockofPLL1(SYSCLK2)andanoutputclockof

theUSBPHY.

NOTE

ForproperUSBfunction,SYSCLK2mustbegreaterthan60MHz.

TheUSBPHYtakesaninputclockthatisconfigurablebytheUSBPHYclocksourcebits(PHYCLKSRC)

intheUSBPHYcontrolregister(USB_PHY_CTL)intheSystemControlModule.Whena24MHzcrystal

isusedatMXI1/MXO1,setPHYCLKSRCto0.Thiswillpresenta24MHzclocktotheUSBPHY.Whena

36MHzcrystalisusedatMXI1/MXO1,setPHYCLKSRCto1.Thiswillpresenta12MHzclock(36MHz

SubmitDocumentationFeedbackDetailedDeviceDescription71