www.ti.com

PRODUCT PREVIEW

3.3.2ExternalMemories

3.3.3Peripherals

3.4ARMInterruptController(AINTC)

3.4.1InterruptMapping

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

TheARMhasaccesstothefollowingExternalmemories:

•DDR2/mDDRSynchronousDRAM

•AsynchronousEMIF/OneNAND

•NANDFlash

•Flashcarddevices:

–MMC/SD

–xD

–SmartMedia

TheARMhasaccesstoalloftheperipheralsonthedevice.

TheDM355ARMInterruptController(AINTC)hasthefollowingfeatures:

•Supportsupto64interruptchannels(16externalchannels)

•Interruptmaskforeachchannel

•EachinterruptchannelcanbemappedtoaFastInterruptRequest(FIQ)ortoanInterruptRequest

(IRQ)typeofinterrupt.

•Hardwareprioritizationofsimultaneousinterrupts

•Configurableinterruptpriority(2levelsofFIQand6levelsofIRQ)

•Configurableinterruptentrytable(FIQandIRQprioritytableentry)toreduceinterruptprocessingtime

TheARMcoresupportstwointerrupttypes:FIQandIRQ.SeetheARM926EJ-STechnicalReference

ManualfordetailedinformationabouttheARM’sFIQandIRQinterrupts.Eachinterruptchannelis

mappabletoanFIQortoanIRQtypeofinterrupt,andeachchannelcanbeenabledordisabled.The

INTCsupportsuser-configurableinterrupt-priorityandinterruptentryaddresses.Entryaddressesminimize

thetimespentjumpingtointerruptserviceroutines(ISRs).Whenaninterruptoccurs,thecorresponding

highestpriorityISR’saddressisstoredintheINTC’sENTRYregister.TheIRQorFIQinterruptroutinecan

readtheENTRYregisterandjumptothecorrespondingISRdirectly.Thus,theARMdoesnotrequirea

softwaredispatchertodeterminetheassertedinterrupt.

TheAINTCtakesupto64ARMdeviceinterruptsandmapsthemtoeithertheIRQortotheFIQofthe

ARM.Eachinterruptisalsoassignedoneof8prioritylevels(2forFIQ,6forIRQ).Forinterruptswiththe

sameprioritylevel,thepriorityisdeterminedbythehardwareinterruptnumber(thelowestnumberhasthe

highestpriority).Table3-1showstheconnectionofdeviceinterruptstotheARM.

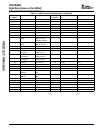

Table3-1.AINTCInterruptConnections

(1)

InterruptAcronymSourceInterruptAcronymSource

NumberNumber

0VPSSINT0VPSS-INT0,32TINT0Timer0-TINT12

Configurablevia

VPSSBLregister:

INTSEL

1VPSSINT1VPSS-INT133TINT1Timer0-TINT34

2VPSSINT2VPSS-INT234TINT2Timer1-TINT12

3VPSSINT3VPSS-INT335TINT3Timer1-TINT34

4VPSSINT4VPSS-INT436PWMINT0PWM0

(1)ThetotalnumberofinterruptsinDM355exceeds64,whichisthemaximumvalueoftheAINTCmodule.Therefore,severalinterrupts

aremultiplexedandyoumustusetheregisterARM_INTMUXintheSystemControlModuletoselecttheinterruptsourceformultiplexed

interrupts.RefertotheARMSubsystemGuideformoreinformationontheSystemControlModuleregisterARM_INTMUX.

SubmitDocumentationFeedbackDetailedDeviceDescription63