www.ti.com

PRODUCT PREVIEW

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

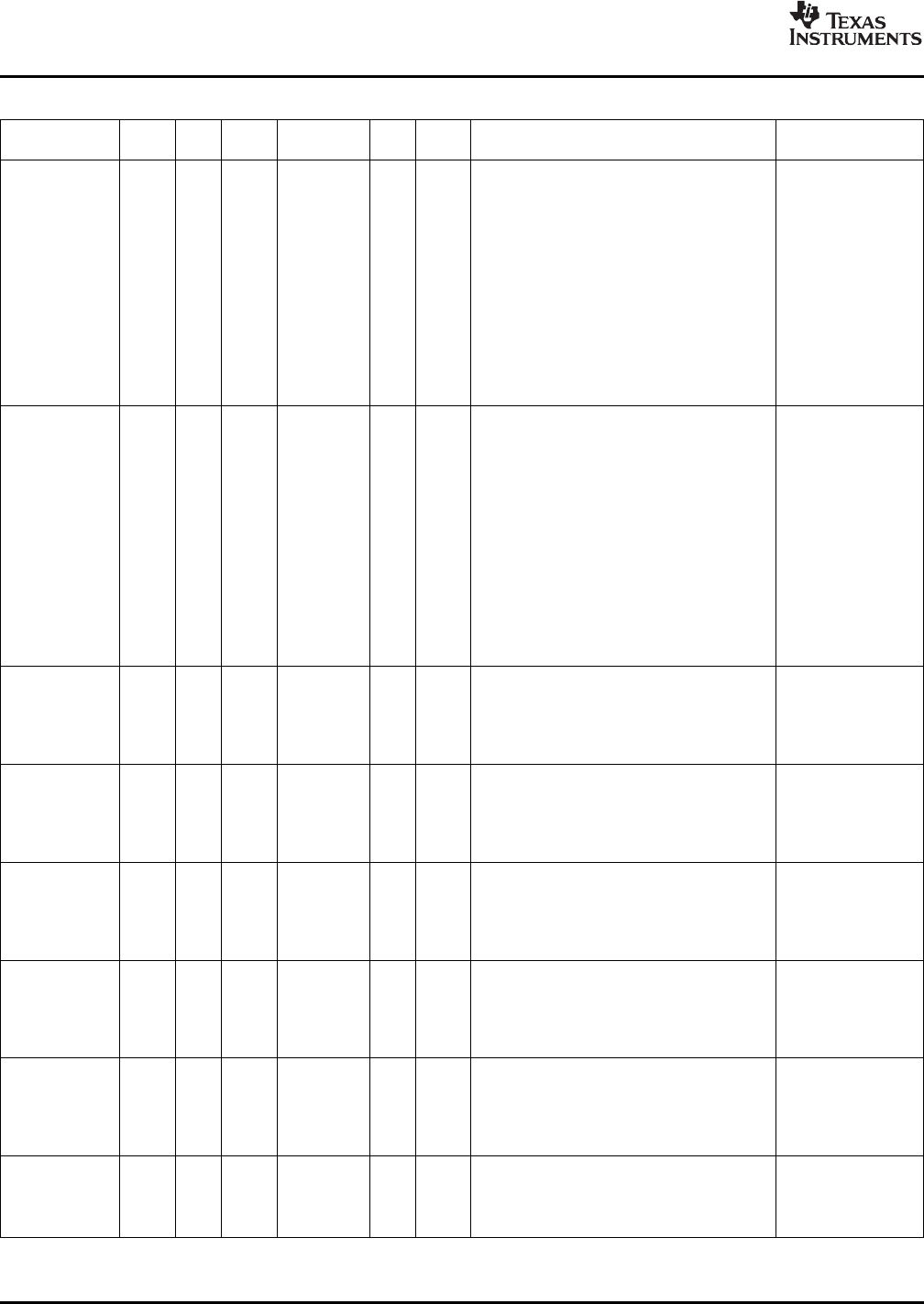

Table2-23.DM355PinDescriptions(continued)

NameBGATypeGroupPowerPUResetDescription

(4)

MuxControl

ID

(1)

Supply

(2)

PD

(3)

State

EM_A09/P17I/OAEMIV

DD

PDinLAsyncEMIF:AddressBusbit[09]PINMUX2[0].EM_A1

GIO063/F/3_3,

AECFG[1]GIO/

syste

m

GIO:GIO[063]defaultsetby

AECFG[0]

System:AECFG[3:0]sampledat

Power-on-ResettosetAEMIFConfiguration

AECFG[2:1]setsdefaultfor

PinMux2.EM_BA0:AEMIFEM_BA0

Definition(00:EM_BA0,01:EM_A14,

10:GIO[054],11:rsvd)

EM_A08/T19I/OAEMIV

DD

PUinHAsyncEMIF:AddressBusbit[08]PINMUX2[0].EM_A1

GIO062/F/3_3,

AECFG[0]GIO/

syste

m

GIO:GIO[062]defaultsetby

AECFG[0]

AECFG[0]setsdefaultfor

-PinMux2.EM_A0_BA1:AEMIFAddress

Width(OneNANDorNAND)

-PinMux2.EM_A13_3:AEMIFAddress

Width(OneNANDorNAND)

(0:AEMIFaddressbits,1:GIO[67:57])

EM_A07/P16I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[07]PINMUX2[0].EM_A1

GIO061F/3_3,

GIO

GIO:GIO[061]-UsedbyROMBootloadertodefaultsetby

provideprogressstatusviaLED(activelow)AECFG[0]

EM_A06/P18I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[06]PINMUX2[0].EM_A1

GIO060F/3_3,

GIO

GIO:GIO[060]defaultsetby

AECFG[0]

EM_A05/R19I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[05]PINMUX2[0].EM_A1

GIO059F/3_3,

GIO

GIO:GIO[059]defaultsetby

AECFG[0]

EM_A04/P15I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[04]PINMUX2[0].EM_A1

GIO058F/3_3,

GIO

GIO:GIO[058]defaultsetby

AECFG[0]

EM_A03/N18I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[03]PINMUX2[0].EM_A1

GIO057F/3_3,

GIO

GIO:GIO[057]defaultsetby

AECFG[0]

EM_A02N15I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[02]

F

NAND/SM/xD:CLE-CommandLatch

Enableoutput

DeviceOverview 44SubmitDocumentationFeedback