www.ti.com

PRODUCT PREVIEW

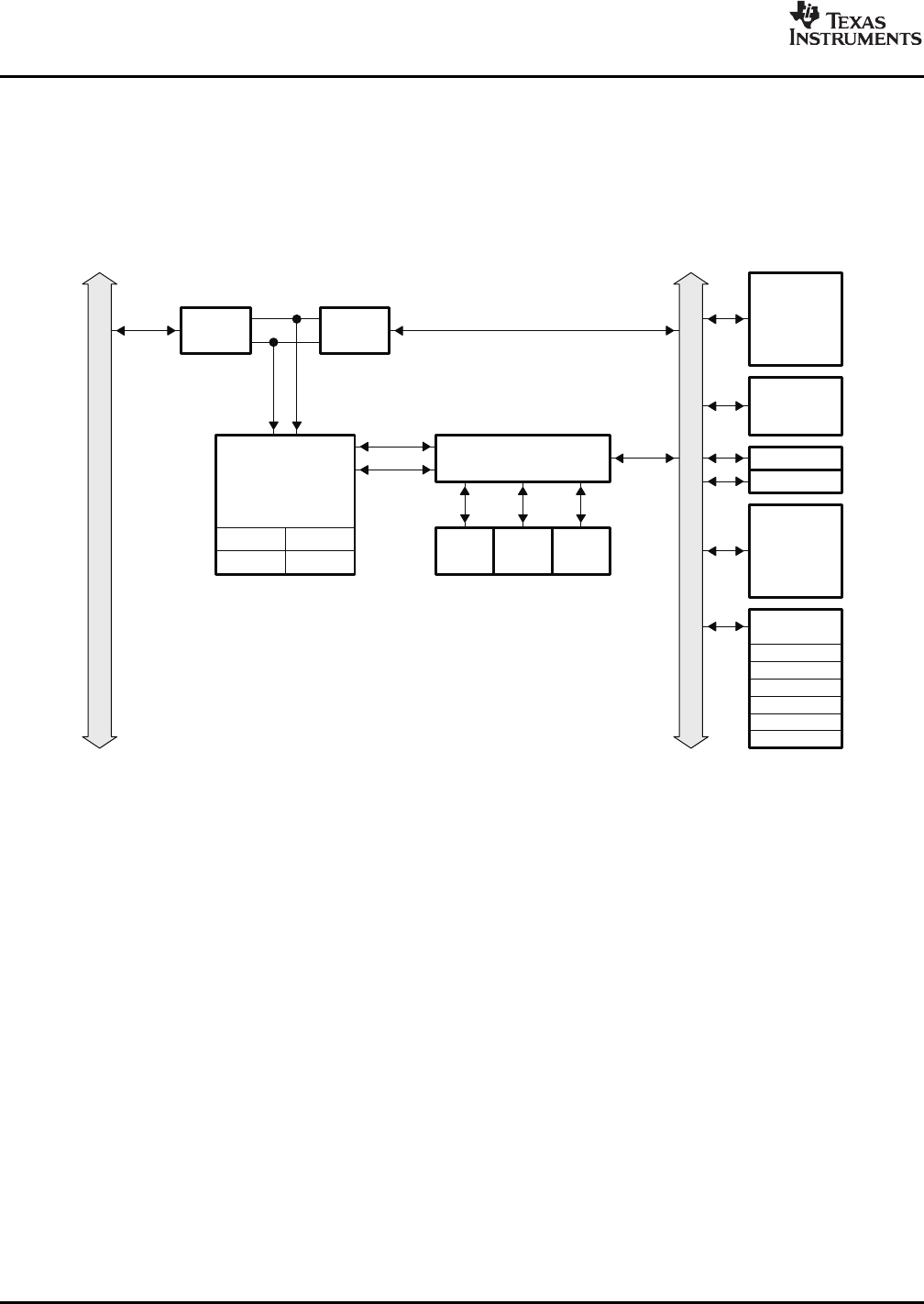

ARM926EJ-S

16KI$

8KD$ MMU

CP15

Arbiter Arbiter

I-AHB

D-AHB

Master

IF

DMAbus

I-TCM

D-TCM

16K

RAM0

RAM1

16K

ROM

8K

Arbiter

Slave

IF

MasterIF

CFGbus

ARM

interrupt

controller

(AINTC)

control

System

PLLC2

PLLC1

(PSC)

controller

sleep

Power

Peripherals

...

3.2ARM926EJ-SRISCCPU

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

–ImagePipe(IPIPE)

–H3AEngine(HardwareengineforcomputingAuto-focus,Autowhitebalance,andAutoexposure)

•VideoProcessingBackEnd(VPBE)

–OnScreenDisplay(OSD)

–VideoEncoderEngine(VENC)

Figure3-1showsthefunctionalblockdiagramoftheDM355ARMSubsystem.

Figure3-1.DM355ARMSubsystemBlockDiagram

TheARMSubsystemintegratestheARM926EJ-Sprocessor.TheARM926EJ-Sprocessorisamemberof

ARM9familyofgeneral-purposemicroprocessors.Thisprocessoristargetedatmulti-taskingapplications

wherefullmemorymanagement,highperformance,lowdiesize,andlowpowerareallimportant.The

ARM926EJ-Sprocessorsupportsthe32-bitARMand16bitTHUMBinstructionsets,enablingtheuserto

tradeoffbetweenhighperformanceandhighcodedensity.Specifically,theARM926EJ-Sprocessor

supportstheARMv5TEJinstructionset,whichincludesfeaturesforefficientexecutionofJavabytecodes,

providingJavaperformancesimilartoJustinTime(JIT)Javainterpreter,butwithoutassociatedcode

overhead.

TheARM926EJ-SprocessorsupportstheARMdebugarchitectureandincludeslogictoassistinboth

hardwareandsoftwaredebug.TheARM926EJ-SprocessorhasaHarvardarchitectureandprovidesa

completehighperformancesubsystem,including:

•ARM926EJ-Sintegercore

•CP15systemcontrolcoprocessor

•MemoryManagementUnit(MMU)

•SeparateinstructionanddataCaches

•Writebuffer

•SeparateinstructionanddataTightly-CoupledMemories(TCMs)[internalRAM]interfaces

•SeparateinstructionanddataAHBbusinterfaces

DetailedDeviceDescription 60SubmitDocumentationFeedback