www.ti.com

PRODUCT PREVIEW

1

PCLK

2

3

7

5

6

4

8

EXTCLK

4

8

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

•InternalColorBarGeneration(100%/75%)

•YUV/RGBmodessupportHDTVoutput(720p/1080i)with74.25MHzexternalclockinput

5.9.2.3VPBEElectricalData/Timing

Table5-21.TimingRequirementsforVPBECLKInputs(seeFigure5-27)

DM355

NO.UNIT

MINMAX

1t

c(PCLK)

Cycletime,PCLK

(1)

13.33160ns

2t

w(PCLKH)

Pulseduration,PCLKhigh5.7ns

3t

w(PCLKL)

Pulseduration,PCLKlow5.7ns

4t

t(PCLK)

Transitiontime,PCLK3ns

5t

c(EXTCLK)

Cycletime,EXTCLK13.33160ns

6t

w(EXTCLKH)

Pulseduration,EXTCLKhigh5.7ns

7t

w(EXTCLKL)

Pulseduration,EXTCLKlow5.7ns

8t

t(EXTCLK)

Transitiontime,EXTCLK3ns

(1)WhentheCCDCisused,thePCLKfrequencymustbelessthanorequaltohalftheVPSSclockfrequency—i.e.,PCLK≤SYSCLK4/2.

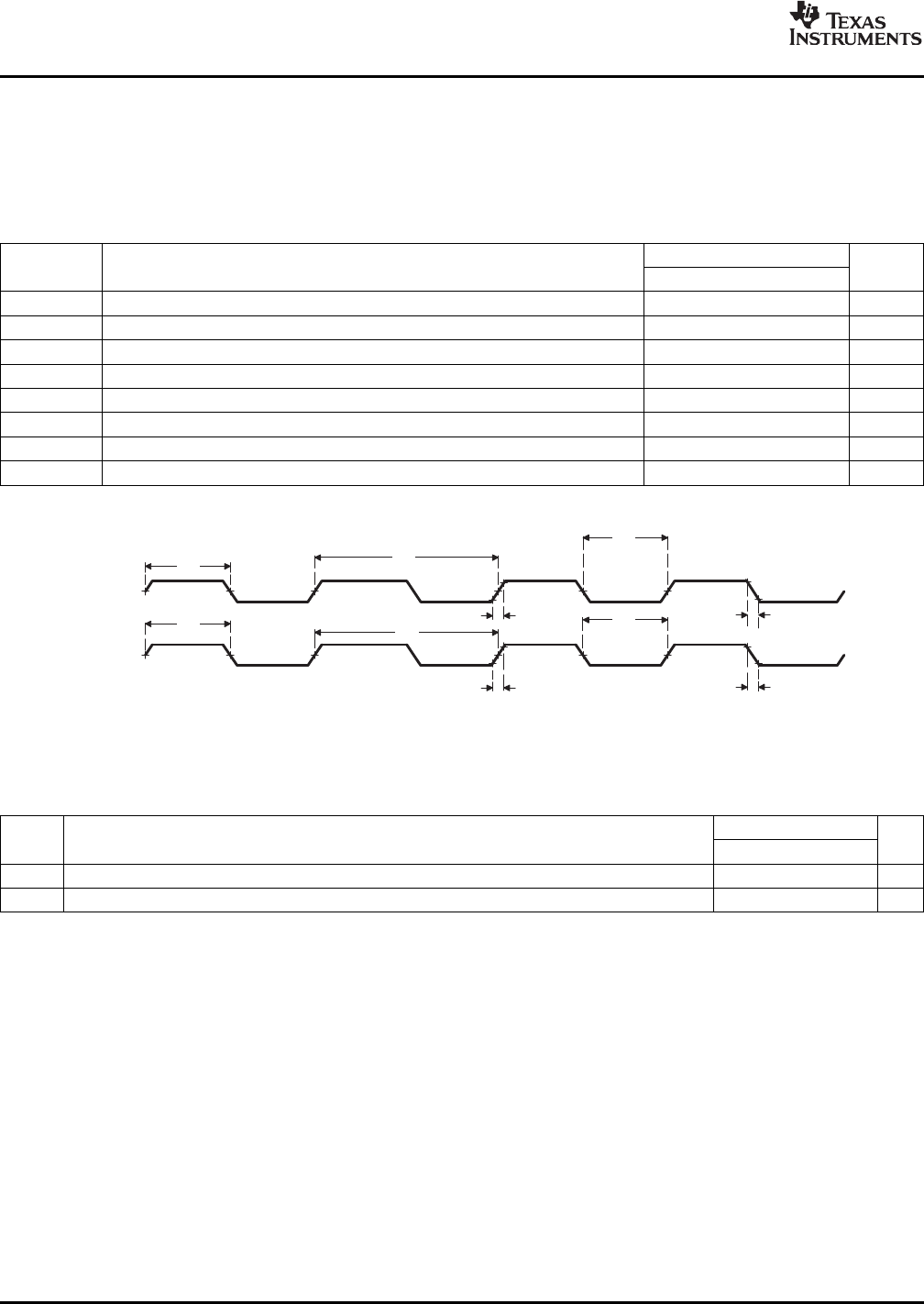

Figure5-27.VPBEPCLKandEXTCLKTiming

Table5-22.TimingRequirementsforVPBEControlInputWithRespecttoPCLKandEXTCLK

(1)(2)(3)

(see

Figure5-28)

DM355

NO.UNIT

MINMAX

9t

su(VCTLV-VCLKIN)

Setuptime,VCTLvalidbeforeVCLKINedge2ns

10t

h(VCLKIN-VCTLV)

Holdtime,VCTLvalidafterVCLKINedge1ns

(1)TheVPBEmaybeconfiguredtooperateineitherpositiveornegativeedgeclockingmode.Wheninpositiveedgeclockingmode,the

risingedgeofVCLKINisreferenced.Wheninnegativeedgeclockingmode,thefallingedgeofVCLKINisreferenced.

(2)VCTL=HSYNC,VSYNC,andFIELD

(3)VCLKIN=PCLKorEXTCLK

PeripheralInformationandElectricalSpecifications 122SubmitDocumentationFeedback