www.ti.com

PRODUCT PREVIEW

3.9PinMultiplexing

3.9.1HardwareControlledPinMultiplexing

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

•Powermanagement

–DeepsleepandfastNANDbootcontrol

•BandwidthManagement

–BusmasterDMAprioritycontrol

FormoreinformationontheSystemControlModulerefertotheARMSubsystemUser'sGuide.

TheDM355makesextensiveuseofpinmultiplexingtoaccommodatethelargenumberofperipheral

functionsinthesmallestpossiblepackage.Inordertoaccomplishthis,pinmultiplexingiscontrolledusing

acombinationofhardwareconfiguration(atdevicereset)andsoftwarecontrol.Noattemptismadebythe

DM355hardwaretoensurethattheproperpinmuxinghasbeenselectedfortheperipheralsorinterface

modebeingused,thusproperpinmuxingconfigurationistheresponsibilityoftheboardandsoftware

designers.AnoverviewofthepinmultiplexingisshowninTable3-12.

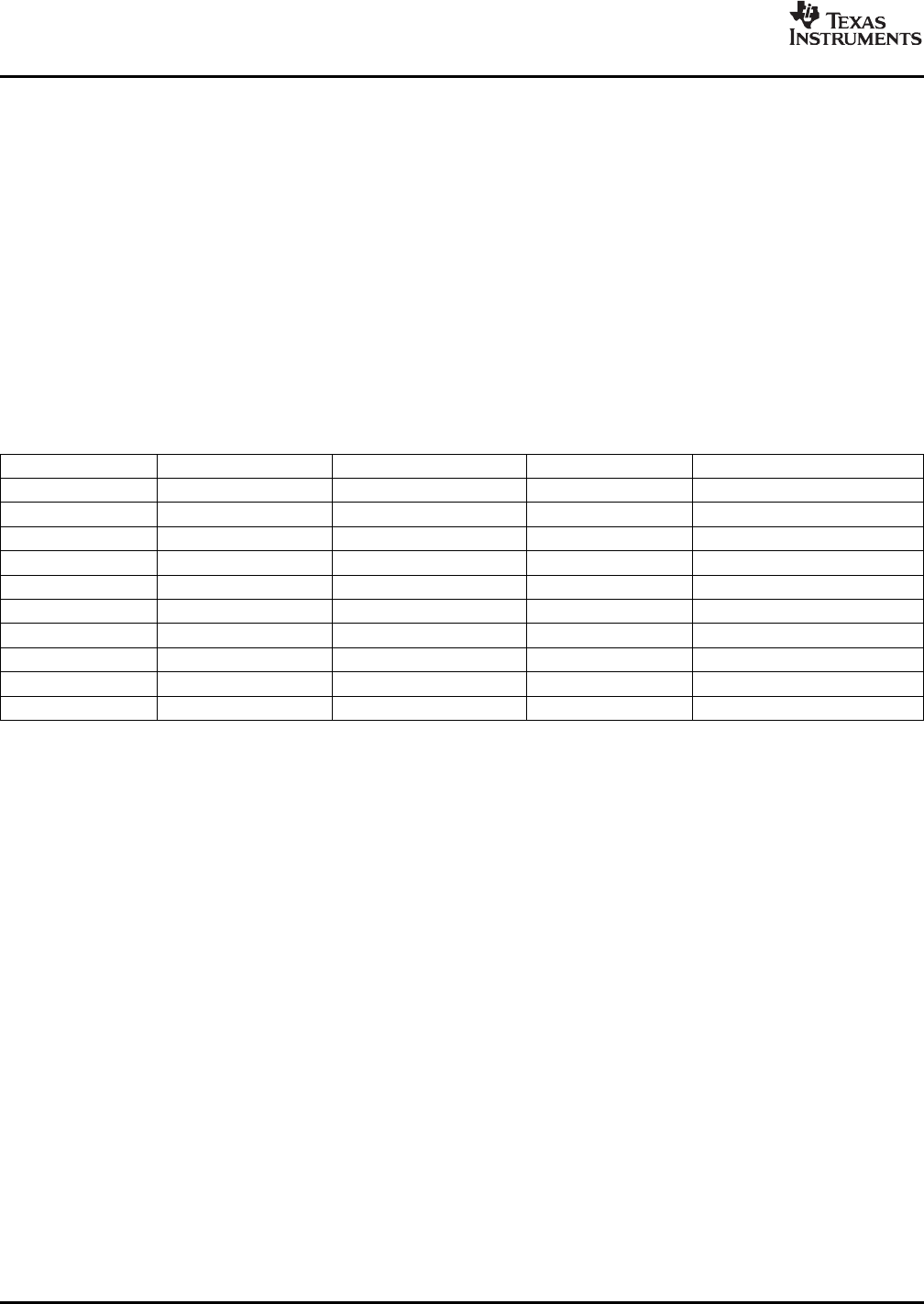

Table3-12.PeripheralPinMuxOverview

PeripheralMuxedWithPrimaryFunctionSecondaryFunctionTertiaryFunction

VPFE(videoin)GPIOandSPI2VPFE(videoin)SPI2GPIO

VPBE(videoout)GPIO,PWM,andRTOVPBE(videoout)PWMandRTOGPIO

AEMIFGPIOAEMIFGPIOnone

ASP0GPIOASP0GPIOnone

MMC/SD1GPIOandUART2MMC/SD1GPIOUART2

CLKOUTGPIOCLKOUTGPIOnone

I2CGPIOI2CGPIOnone

UART1GPIOUART1GPIOnone

SPI1GPIOSPI1GPIOnone

SPI0GPIOSPI0GPIOnone

UsetheAsynchronousEMIFconfigurationpins(AECFG[3:0])forhardwarepinmuxcontrol.AECFG[3:0]

controlthepartitioningoftheAEMIFaddressesandGPIOsatreset,whichallowsyoutoproperly

configurethenumberofAEMIFaddresspinsrequiredbythebootdevicewhileunusedaddressespinsare

availableasGPIOs.ThesesettingsmaybechangedbysoftwareafterresetbyprogrammingthePinMux2

registerThePinMux2registerisintheSystemControlModule.AsshowninTable3-13,thenumberof

addressbitsenabledontheAEMIFisselectablefrom0to16.Pinsthatarenotassignedtoanother

peripheralandnotenabledasaddresssignalsbecomeGPIOs(exceptEM_A[2:1]).Theenabledaddress

signalsarealwayscontiguousfromEM_BA[1]upwards;bitscannotbeskipped.Theexceptiontothisare

EM_A[2:1].Thesesignals(canbeusedto)representtheALEandCLEsignalsfortheNANDFlashmode

oftheAEMIFandarealwaysenabled.NotethatEM_A[0]doesnotrepresentthelowestAEMIFaddress

bit.DM355supportsonly16-bitand8-bitdatawidthsfortheAEMIF.In16-bitmode,EM_BA[1]represents

theLSaddressbit(thehalf-wordaddress)andEM_BA[0]representstheMSaddressbit(A[14]).In8-bit

mode,EM_BA[1:0]representthe2LSaddressbits.Notethatadditionalselectionsareavailableby

programmingthePinMux2registerinsoftwareafterboot.NotethatAECFGselectionof‘0010’selects

OneNANDinterface.TheAEMIFneedstooperateinthehalf-ratemode(full_rate=0)tomeetfrequency

requirements.SoftwareshouldnotchangethePINMUX2registersettingtoaffecttheAEMIFrate

operation.AsoftresetoftheAEMIFshouldbeperformedanytimearatechangeismade.

DetailedDeviceDescription 78SubmitDocumentationFeedback