www.ti.com

PRODUCT PREVIEW

3.1464-BitCrossbarArchitecture

3.14.1CrossbarConnections

3.14.2EDMAController

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

TheDM355usesa64-bitcrossbararchitecturetocontrolaccessbetweendeviceprocessors,subsystems

andperipherals.ItincludesanEDMAControllerconsistingofaDMATransferController(TC)andaDMA

ChannelController(CC).TheTCprovidestwoDMAchannelsfortransferbetweenslaveperipherals.The

CCprovidesauserandeventinterfacetotheEDMAsystem.Itincludesupto64eventchannelstowhich

allsystemsynchronizationeventscanbemappedand8autosubmit“quick”channels(QDMA).Inmost

ways,thesechannelsareidentical.Achannelreferstoaspecific‘event’thatcancauseatransfertobe

submittedtotheTCasaTransferRequest.

Therearefivetransfermasters(TCshaveseparatereadandwriteconnections)connectedtothe

crossbar;ARM,theVideoProcessingSub-system(VPSS),themasterperipherals(USB),andtwoEDMA

transfercontrollers.Thesecanbeconnectedtofourseparateslaveports;ARM,theDDREMIF,andCFG

busperipherals.Notallmastersmayconnecttoallslaves.Connectionpathsareindicatedby√at

intersectionpointsshowninTable3-18

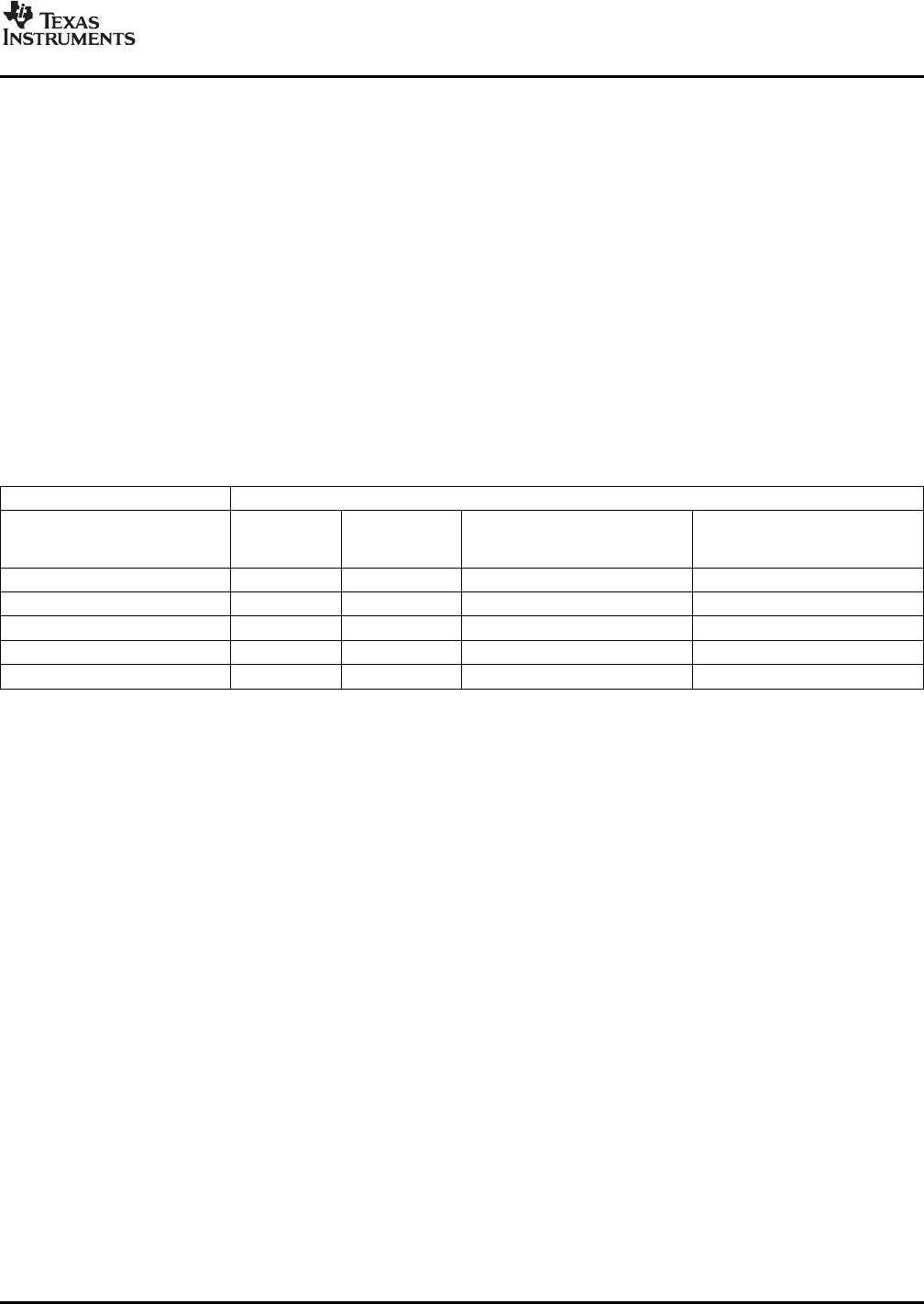

Table3-18.CrossbarConnectionMatrix

SlaveModule

DMAMasterARMInternalMPEG/JPEGConfigBusRegistersandDDREMIFMemory

MemoryCo-processorMemory

Memory

ARM√√√√

VPSS√

DMAMasterPeripherals(USB)√√

EDMA3TC0√√√√

EDMA3TC1√√√√

TheEDMAcontrollerhandlesalldatatransfersbetweenmemoriesandthedeviceslaveperipheralson

theDM355device.Thesearesummarizedasfollows:

•Transferto/fromon-chipmemories

–ARMprogram/dataRAM

–MPEG/JPEGCo-processormemory

•Transferto/fromexternalstorage

–DDR2/mDDRSDRAM

–AsynchronousEMIF

–OneNANDflash

–NANDflash

–SmartMedia,SD,MMC,xDmediastorage

•Transferto/fromperipherals

–ASP

–SPI

–I2C

–PWM

–RTO

–GPIO

–Timer/WDT

–UART

–MMC/SD

SubmitDocumentationFeedbackDetailedDeviceDescription87