www.ti.com

PRODUCT PREVIEW

5PeripheralInformationandElectricalSpecifications

5.1ParameterInformationDevice-SpecificInformation

TransmissionLine

4.0pF 1.85pF

Z0=50Ω

(seenote)

Tester PinElectronics

Data SheetTimingReferencePoint

Output

Under

Test

42 Ω 3.5nH

DevicePin

(seenote)

5.1.1SignalTransitionLevels

V

ref

V

ref

=V

IL

MAX(orV

OL

MAX)

V

ref

=V

IH

MIN(orV

OH

MIN)

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

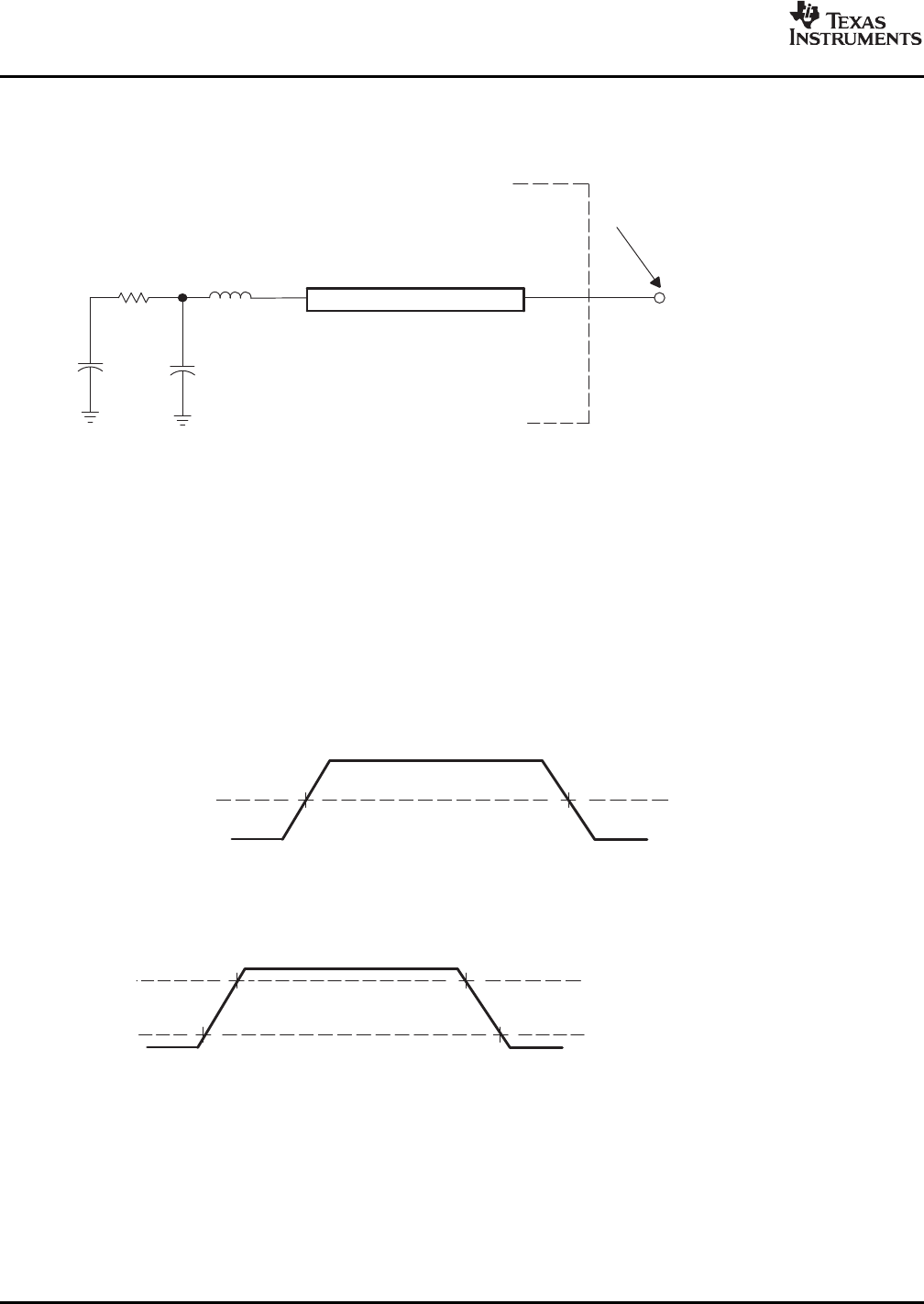

A.Thedatasheetprovidestimingatthedevicepin.Foroutputtiminganalysis,thetesterpinelectronicsandits

transmissionlineeffectsmustbetakenintoaccount.Atransmissionlinewithadelayof2nsorlongercanbeusedto

producethedesiredtransmissionlineeffect.Thetransmissionlineisintendedasaloadonly.Itisnotnecessaryto

addorsubtractthetransmissionlinedelay(2nsorlonger)fromthedatasheettimings.

Inputrequirementsinthisdatasheetaretestedwithaninputslewrateof<4Voltspernanosecond(4V/ns)atthe

devicepin.

Figure5-1.TestLoadCircuitforACTimingMeasurements

TheloadcapacitancevaluestatedisonlyforcharacterizationandmeasurementofACtimingsignals.This

loadcapacitancevaluedoesnotindicatethemaximumloadthedeviceiscapableofdriving.

AllinputandoutputtimingparametersarereferencedtoV

ref

forboth"0"and"1"logiclevels.For3.3VI/O,

V

ref

=1.65V.For1.8VI/O,V

ref

=0.9V.

Figure5-2.InputandOutputVoltageReferenceLevelsforACTimingMeasurements

AllriseandfalltransitiontimingparametersarereferencedtoV

IL

MAXandV

IH

MINforinputclocks,

V

OL

MAXandV

OH

MINforoutputclocks.

Figure5-3.RiseandFallTransitionTimeVoltageReferenceLevels

94PeripheralInformationandElectricalSpecificationsSubmitDocumentationFeedback