www.ti.com

PRODUCT PREVIEW

3.5.2SupportedClockingConfigurationsforDM355-216

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

ThissectiondescribestheonlysupporteddeviceclockingconfigurationsforDM355-216.TheDM355

supportseither24MHz(typical)or36MHzreferenceclock(crystalorexternaloscillatorinput).

Configurationsareshownforbothcases.

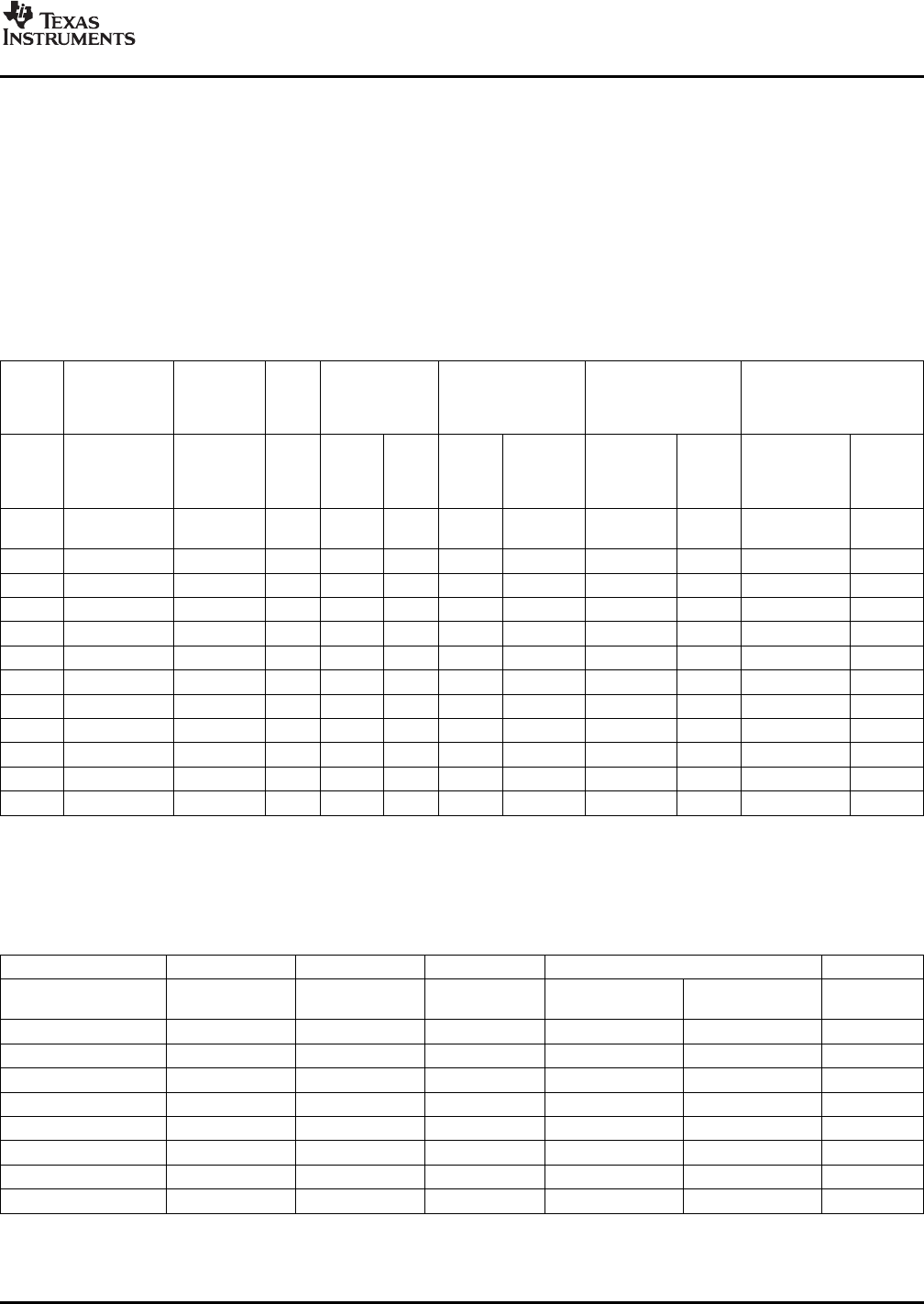

3.5.2.1SupportedClockingConfigurationsforDM355-216(24MHzreference)

3.5.2.1.1DM355-216PLL1(24MHzreference)

AllsupportedclockingconfigurationsforDM355-216PLL1with24MHzreferenceclockareshownin

Table3-2

Table3-2.PLL1SupportedClockingConfigurationsforDM355-216(24MHzreference)

PREDIPLLMPOSTDIVPLL1ARM/PeripheralsVencVPSS

VVCOMPEGand

JPEG

Co-Processor

(/8(m(/2or/1(MHz)PLLDIVSYSCPLLDIVSYSCLK2PLLDIV3SYSCLPLLDIV4SYSCLK

fixed)programmableprogramma1LK12(MHz)(/nK3(/4or/24

)ble)(/2(MHz)(/4programma(MHz)programmable(MHz)

fixed)fixed)ble))

bypassbypassbypassbypas21246102.446

s

814414322216410816274108

813514052202.54101.2515274101.25

812613782189494.51427494.5

811713512175.5487.751327487.75

8108132421624811227481

89912972148.5474.251127474.25

818022702135467.510272135

816222432121.5460.759272121.5

8144221621084548272108

81262189294.5447.25727294.5

81082162281440.5627281

3.5.2.1.2DM355-216PLL2(24MHzreference)

AllsupportedclockingconfigurationsforDM355-216PLL2with24MHzreferenceclockareshownin

Table3-3

Table3-3.PLL2SupportedClockingConfigurationsforDM355-216(24MHzreference)

PREDIVPLLMPOSTDIVPLL2VCODDRPHYDDRClock

(/nprogrammable)(m(/1fixed)(MHz)PLLDIV1SYSCLK1DDR_CLK

programmable)(/1fixed)(MHz)(MHz)

bypassbypassbypassbypass12412

811413421342171

810813241324162

810213061306153

89612881288144

1213312661266133

1210012001200100

151001160116080

SubmitDocumentationFeedbackDetailedDeviceDescription67