www.ti.com

PRODUCT PREVIEW

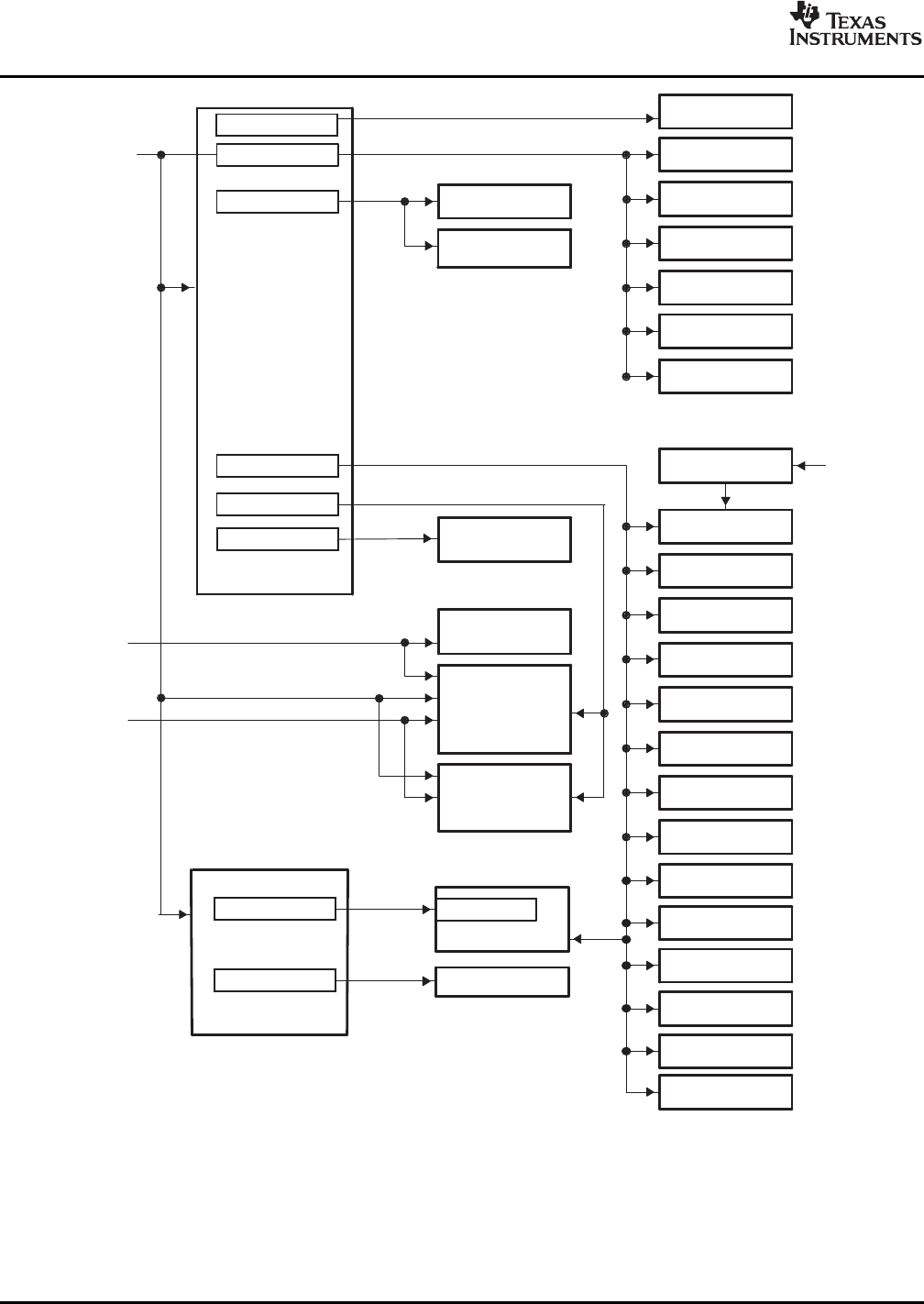

ARMsubsystem

MPEG/JPEG

Coprocessor

SYSCLK1

SYSCLK2

VPFE

VPBE

DAC

DDRPHY

DDR

PLLDIV1(/1)

BPDIV(/8)

PLL controller2

PLL controller1

PLLDIV3(/n)

PLLDIV2(/4)

PLLDIV1(/2)

SYSCLK3

I2C

Timers(x4)

PWMs(x4)

SPI(x3)

MMC/SD(x2)

EMIF/NAND

ASP (x2)

GPIO

UART2

ARMINTC

USB

60MHz

Reference

clock

(MXI/MXO)

(24MHzor

36MHz)

Referenceclock

(MXI/MXO)

24MHzor36Mhz

PCLK

AUXCLK(/1)

BPDIV(/3)

SYSCLK1

CLKOUT3

SYSCLKBP

CLKOUT2

EDMA

Buslogic

Syslogic

PSC

IcePick

EXTCLK

RTO

USBPhy

SYSCLKBP

AUXCLK

PLLDIV4(/4or/2)

VPSS

UART0,1

CLKOUT1

Sequencer

SYSCLK4

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

Figure3-2.DeviceClockingBlockDiagram

66DetailedDeviceDescriptionSubmitDocumentationFeedback