www.ti.com

PRODUCT PREVIEW

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

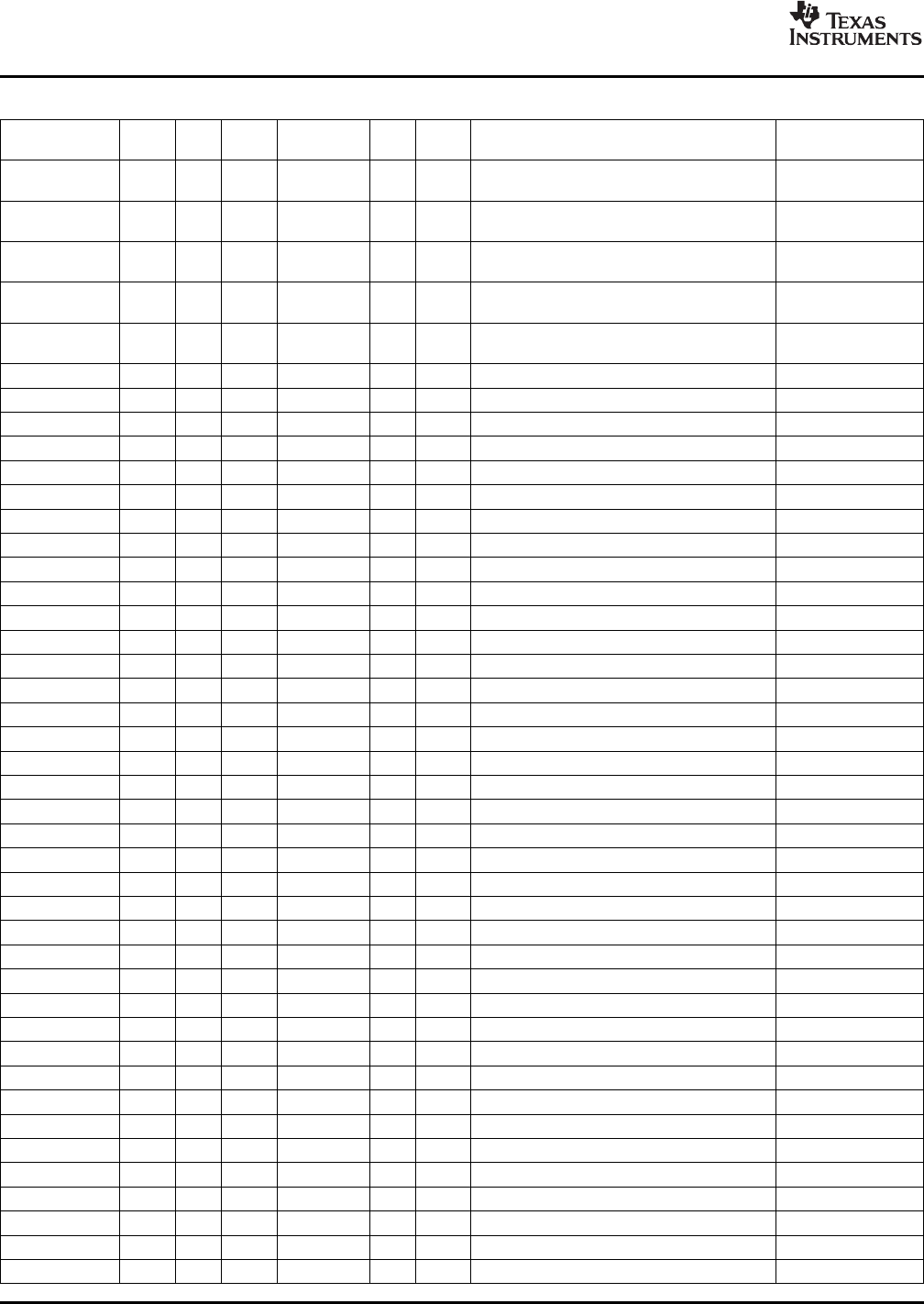

Table2-23.DM355PinDescriptions(continued)

NameBGATypeGroupPowerPUResetDescription

(4)

MuxControl

ID

(1)

Supply

(2)

PD

(3)

State

RSV03L1AReserved.ThissignalshouldbeleftasaNo

I/O/ZConnectorconnectedtoV

SS

.

RSV04M1AReserved.ThissignalshouldbeleftasaNo

I/O/ZConnectorconnectedtoV

SS

.

RSV05N2AReserved.Thissignalshouldbeconnected

I/O/ZtoV

SS

.

RSV06M2PWRReserved.Thissignalshouldbeconnected

toV

SS

.

RSV07K2GNDReserved.Thissignalshouldbeconnected

toV

SS

.

NCH8Noconnect

V

DD_VIN

P6PWRPowerforDigitalVideoInputIO(3.3V)

V

DD_VIN

P7PWRPowerforDigitalVideoInputIO(3.3V)

V

DD_VIN

P8PWRPowerforDigitalVideoInputIO(3.3V)

V

DD_VOUT

F6PWRPowerforDigitalVideoOutputIO(3.3V)

V

DD_VOUT

F7PWRPowerforDigitalVideoOutputIO(3.3V)

V

DD_VOUT

F8PWRPowerforDigitalVideoOutputIO(3.3V)

V

DD_DDR

M9PWRPowerforDDRI/O(1.8V)

V

DD_DDR

P9PWRPowerforDDRI/O(1.8V)

V

DD_DDR

P10PWRPowerforDDRI/O(1.8V)

V

DD_DDR

P11PWRPowerforDDRI/O(1.8V)

V

DD_DDR

P12PWRPowerforDDRI/O(1.8V)

V

DD_DDR

P13PWRPowerforDDRI/O(1.8V)

V

DD_DDR

P14PWRPowerforDDRI/O(1.8V)

V

DD_DDR

R9PWRPowerforDDRI/O(1.8V)

V

DD_DDR

R12PWRPowerforDDRI/O(1.8V)

V

DD_DDR

T14PWRPowerforDDRI/O(1.8V)

V

DDA_PLL1

G12PWRAnalogPowerforPLL1(1.3V)

V

DDA_PLL2

H9PWRAnalogPowerforPLL2(1.3V)

CV

DD

A1PWRCorepower(1.3V)

CV

DD

A10PWRCorepower(1.3V)

CV

DD

B19PWRCorepower(1.3V)

CV

DD

C4PWRCorepower(1.3V)

CV

DD

G6PWRCorepower(1.3V)

CV

DD

G11PWRCorepower(1.3V)

CV

DD

H10PWRCorepower(1.3V)

CV

DD

H13PWRCorepower(1.3V)

CV

DD

H17PWRCorepower(1.3V)

CV

DD

J11PWRCorepower(1.3V)

CV

DD

J12PWRCorepower(1.3V)

CV

DD

J13PWRCorepower(1.3V)

CV

DD

K6PWRCorepower(1.3V)

CV

DD

K11PWRCorepower(1.3V)

CV

DD

K12PWRCorepower(1.3V)

CV

DD

L11PWRCorepower(1.3V)

CV

DD

L12PWRCorepower(1.3V)

CV

DD

N6PWRCorepower(1.3V)

CV

DD

R7PWRCorepower(1.3V)

DeviceOverview 52SubmitDocumentationFeedback