www.ti.com

PRODUCT PREVIEW

TMS320DM355

DigitalMediaSystem-on-Chip(DMSoC)

SPRS463A–SEPTEMBER2007–REVISEDSEPTEMBER2007

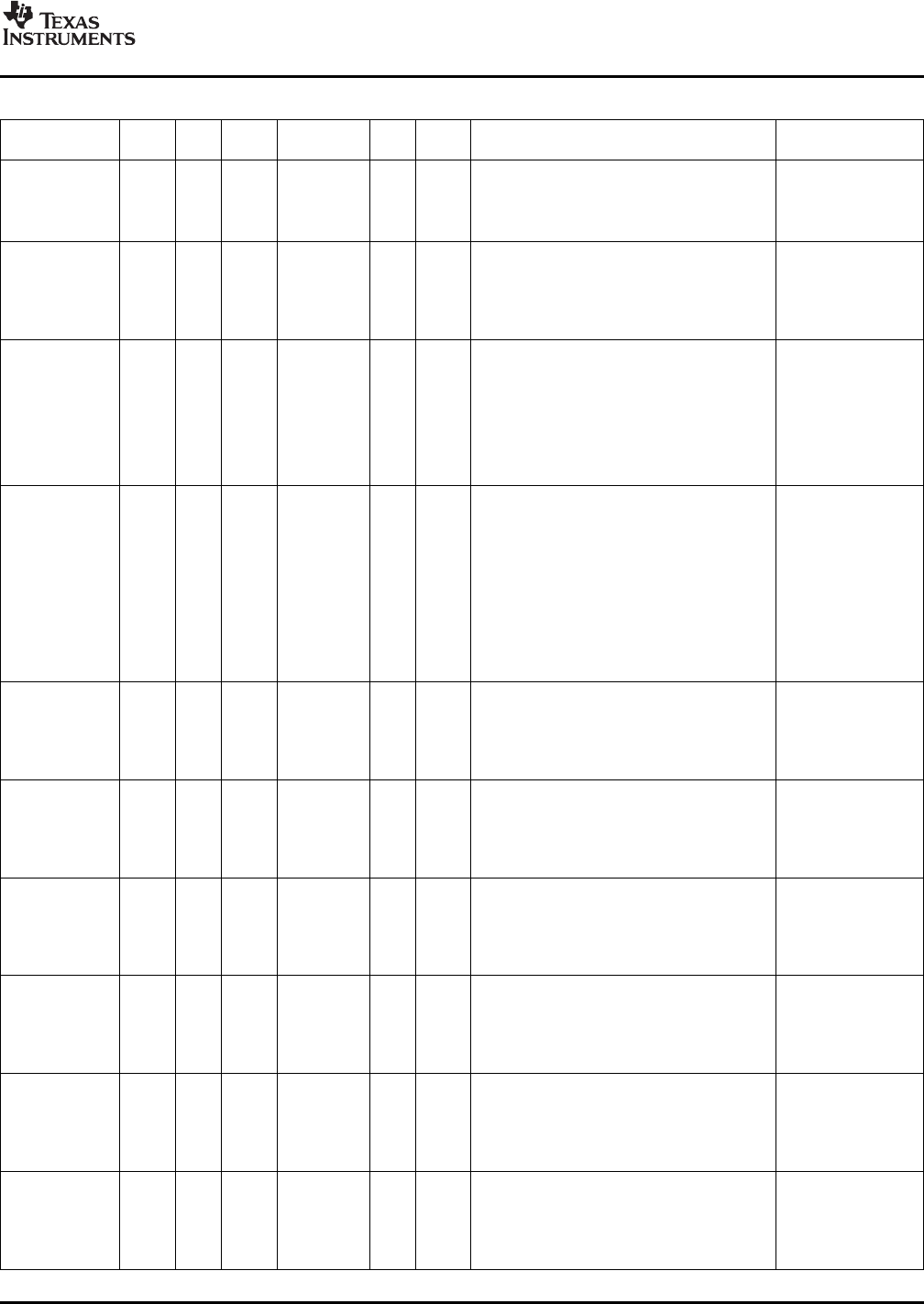

Table2-23.DM355PinDescriptions(continued)

NameBGATypeGroupPowerPUResetDescription

(4)

MuxControl

ID

(1)

Supply

(2)

PD

(3)

State

EM_A01N17I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[01]

F

NAND/SM/xD:ALE-AddressLatchEnable

output

EM_A00/M16I/OAEMIV

DD

outLAsyncEMIF:AddressBusbit[00]NotethatPINMUX2[1].EM_A0

GIO056F/theEM_A0isalwaysa32-bitaddress_BA1,

GIO

GIO:GIO[056]defaultsetby

AECFG[0]

EM_BA1/P19I/OAEMIV

DD

outHAsyncEMIF:BankAddress1signal=16-bitPINMUX2[1].EM_A0

GIO055F/address._BA1,

GIO

In16-bitmode,lowestaddressbit.defaultsetby

AECFG[0]

In8-bitmode,secondlowestaddressbit

GIO:GIO[055]

EM_BA0/N19I/OAEMIV

DD

outHAsyncEMIF:BankAddress0signal=8-bitPINMUX2[3:2].EM_

GIO054/F/address.BA0,

EM_A14GIO/

EMIF2

.30

In8-bitmode,lowestaddressbit.defaultsetby

AECFG[2:1]

Or,canbeusedasanextraAddressline

(bit[14]whenusing16-bitmemories.

GIO:GIO[054]

EM_D15/M18I/OAEMIV

DD

inAsyncEMIF:DataBusbit[15]PINMUX2[4].EM_D1

GIO053F/5_8,

GIO

GIO:GIO[053]defaultsetby

AECFG[3]

EM_D14/M19I/OAEMIV

DD

inAsyncEMIF:DataBusbit[14]PINMUX2[4].EM_D1

GIO052F/5_8,

GIO

GIO:GIO[052]defaultsetby

AECFG[3]

EM_D13/M15I/OAEMIV

DD

inAsyncEMIF:DataBusbit[13]PINMUX2[4].EM_D1

GIO051F/5_8,

GIO

GIO:GIO[051]defaultsetby

AECFG[3]

EM_D12/L18I/OAEMIV

DD

inAsyncEMIF:DataBusbit[12]PINMUX2[4].EM_D1

GIO050F/5_8,

GIO

GIO:GIO[050]defaultsetby

AECFG[3]

EM_D11/L17I/OAEMIV

DD

inAsyncEMIF:DataBusbit[11]PINMUX2[4].EM_D1

GIO049F/5_8,

GIO

GIO:GIO[049]defaultsetby

AECFG[3]

EM_D10/L19I/OAEMIV

DD

inAsyncEMIF:DataBusbit[10]PINMUX2[4].EM_D1

GIO048F/5_8,

GIO

GIO:GIO[048]defaultsetby

AECFG[3]

SubmitDocumentationFeedbackDeviceOverview45