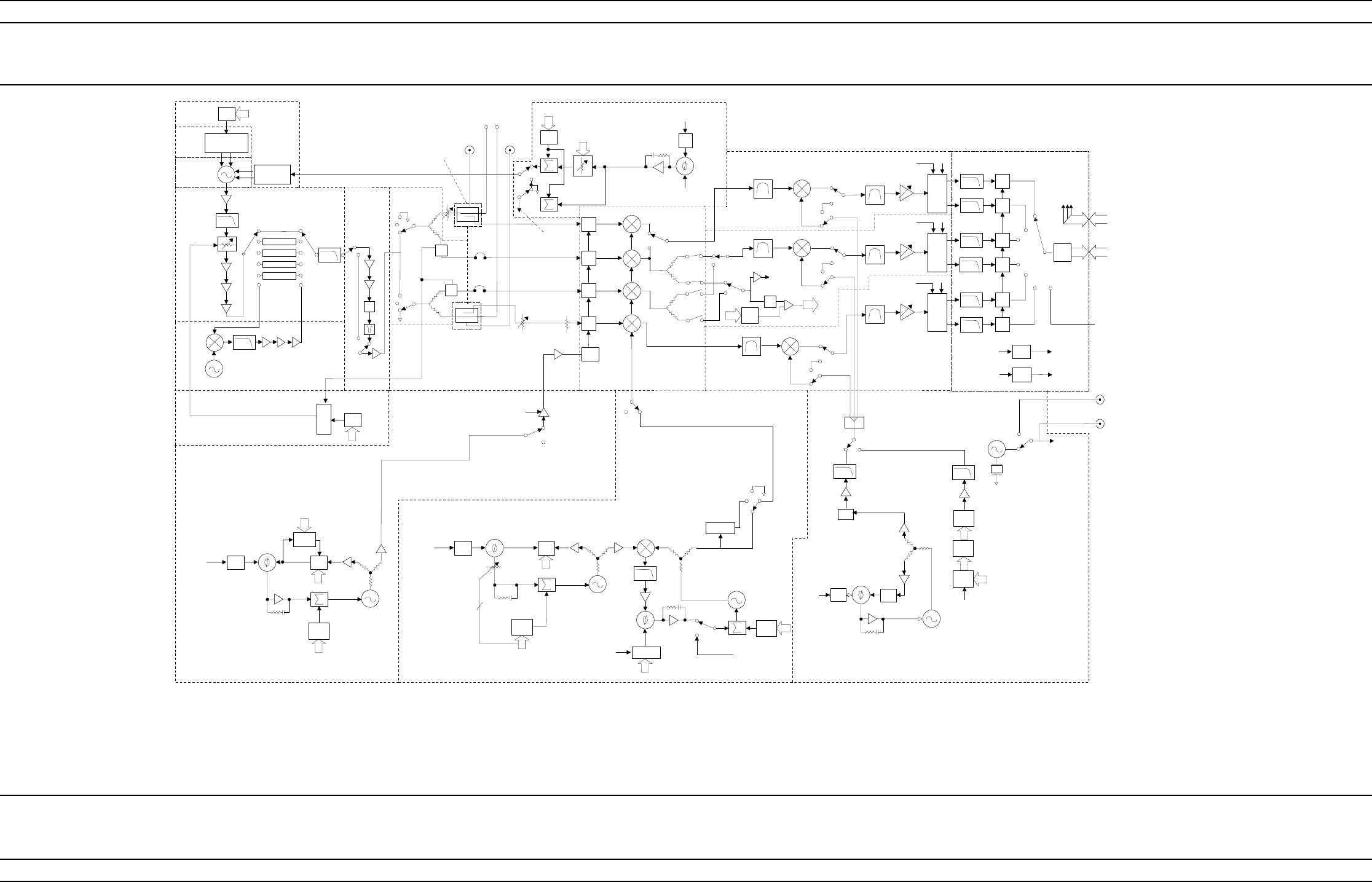

7-6 373XXA MM

SYSTEM OVERVIEW SYSTEM DESCRIPTION

P2 BIAS

P1

D/A

P2

D/A

80KHz

÷20

÷M

÷10

÷K

1MHz

D/A

207-403MHz

1MHz RES

10 MHz

2 BITS

NCO

10 MHz

QB*

QB*

QB*

QB*

QB*

QB*

QB*

QB*

QB*

9-10MHz

1Hz RES

D/A

SOURCE

TRACK

(A8)

197-394M

1Hz RES

÷2,4,8

25.0-272.5MHz

1Hz RES

25.0-272.5MHz

1HZ RES

÷20

÷121

400K

10 MHz

÷25

48.4MHz

2.42MHz

CAL

80KHz

D/A

SIN

ROM

÷125

10 MHz

EXT 10M OUT

EXT 10M IN

EXT

INT

10 MHz

A1

1

ST

LO

A2

2

ND

LO

A7

3

RD

LO

H

10 MHz

-6MHz/V

A21A2

SOURCE

CONTROL

H

IRM

RA

RFF

RB

SOURCE LOCK

(A4)

SOURCE

LOCK (A8)

LVL

DET

LVL

THR

DAC

P1 BIAS

10 MHz

2.5 MHz

TA

RA

RB

TB

TA

RA

2.5M

2.5M

2.5M

S

S

S

S

SD

SD

SD

A/D

S/H

S/H

S/H

S/H

CTL

A/D Bus

Quiet Bus

S/H

S/H

SWITCHED IF BW

10Hz-10KHz

D/A QB*

MAIN

COIL DRIVER

A21A2

SOURCE

CONTROL

A21A1

SOURCE

YIG/BIAS

2-20GHz

YIG

FM

DRIVER

SWITCHED

FILTER

13.5GHz LPF

8.4GHz LPF

5.5GHz LPF

3.3GHz LPF

DOWN

CONVERTER

6.3 GHz FFO

ALC

x2

SDM

(Above 20 GHz

units only))

XFER SWITCH**

R

F

R

F

COUPLER / BIAS TEE

(LF BRIDGES

IN 37217A

AND BELOW)

0-70

LVL

DET

LVL

DET

OPTIONAL

REFERENCE A

EXTENSION

OPTIONAL

REFERENCE B

EXTENSION

0-40

OPTIONAL

SOURCE

TRACK

(A2)

89MHz

89MHz

89MHz

89MHz

A8

SOURCE LOCK / SIGNAL

SEPARATION CONTROL

SRD/SAMP/

BUFFAMP

A6

TEST B IF

CAL

IRM

A4

REF IN

H

CAL

IRM

H

CAL

A3

TEST AIF

80KHz

IF SYNC

10 MHz

IF SYNC

10 MHz

IF SYNC

10 MHz

80KHz

PS

SYNC

IF

SYNC

109.89KHz

80KHz

TO

POWER

SUPPLY

10MHz

10MHz

IF

SYNC

Analog Monitor

±

±

FromA1-A8 andA21A1/A21A2 PCBs

(Diagnostic Measurement Bus)

**Low Frequency Bridges for

Models 37211A& 37217A

*Quiet Bus (fromA14 101 PCB)

A5

A/D

COMB

GENERATOR

POWER

AMP

FRAC

500K

D/A

357-536.5MHz

50KHz RES

10 MHz

HH POWER

357-536.5MHz

50KHz RES

÷

4

372XX17.CDR

** For Models 37377Aand 37397A, see Figures 5-3 and 5-4

Figure 7-2. Analog Subsystem Block Diagram

* Quiet Bus (from A14 PCB)

** Low Frequency Bridges for Models 37311A and 37317A.

± From A1-A8 and A21A1/A21A2 PCBs

(Diagnostic Measurement Bus)