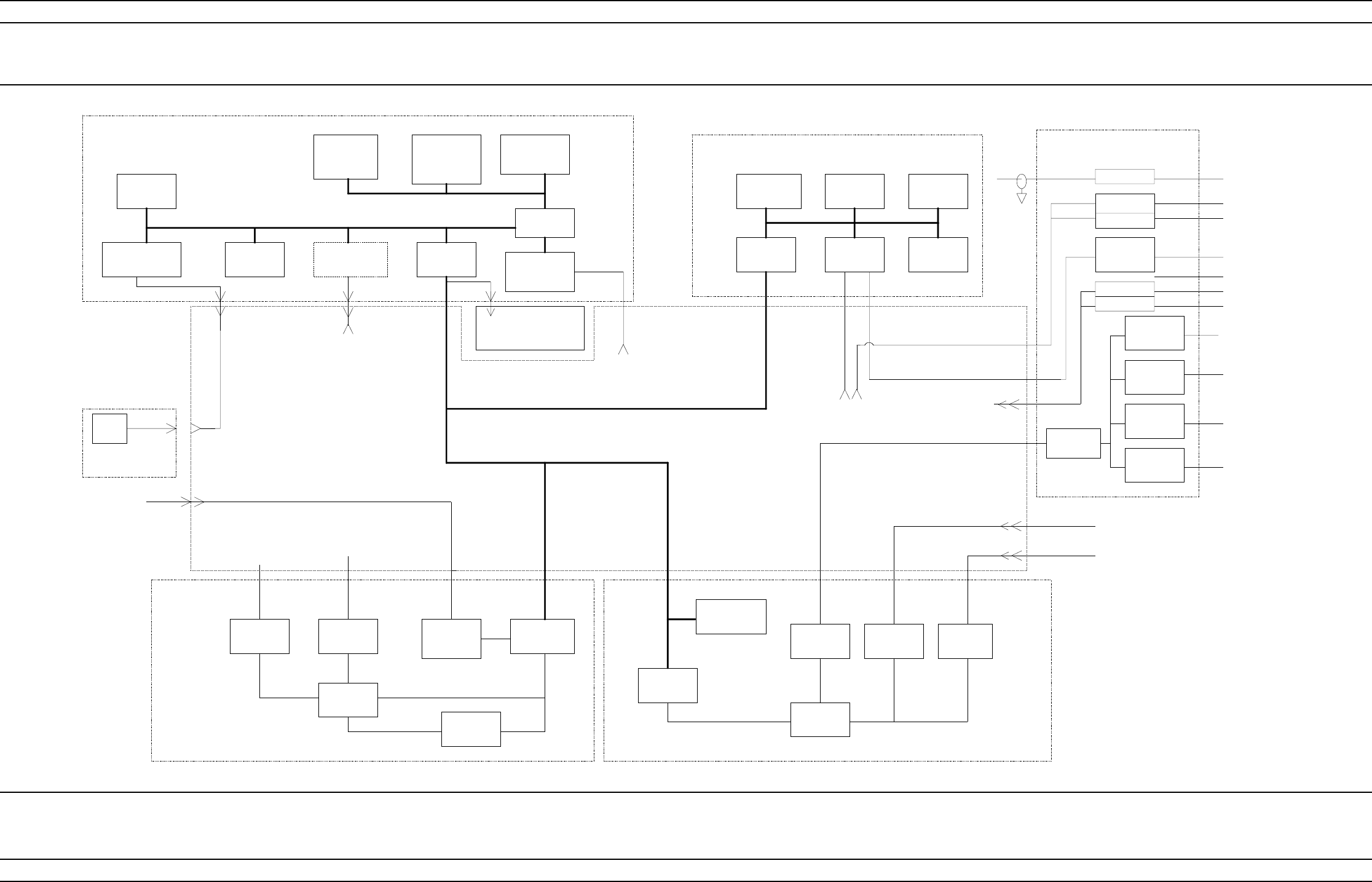

7-14 373XXA MM

DIGITAL SUBSYSTEM ASSEMBLIES SYSTEM DESCRIPTION

BATTERY

BACKED

RAM/CLOCK

EPROM /

FLASH

SRAM

MEMORY

ARRAY WITH

BATTERY

SCSI

COPROCESSOR

68040 Pµ

ETHERNET

CONTROLLER

VMECHIP2

SERIAL I/O

CONTROLLER

VME

TERMINATOR

BOARD

HARD

DISK

A16

HARD DISK PCB

DRAM

MEMORY

ARRAY

MC CHIP

QUIET.

BUS

CONTROL

A/D

BUS

CONTROL

FRONT

PANEL

INTERFACE

VME

INTERFACE

LOGIC /

DECODING

STATE

MACHINE

VME

INTERFACE

REAR

PANEL

INTERFACE

DISK

DRIVE

CONTROL

EXTERNAL

KEYBOARD

CONTROL

LOGIC /

DECODING

VGA

OUT

LIMIT

LINES

PRINTER

INTERFACE

37XXA

GPIB

SYSTEM

GPIB

LOGIC/

DECODING

GRAPHICS

PROCESSOR

INTERRUPT

VECTOR

DRAM

VME

INTERFACE

VIDEO

PALATTE

VRAM

VME

TERMINATIONS

BIAS TEE

ANA OUT

DIGITAL IN

P/O J19*

MOTHERBOARD PCB

A14 I/O 2 PCB

A13 I/O 1 PCB

A15 GRAPHICS PCB

QUIET

BUS

(TO ANALOG

SUBSYSTEM*)

A / D

BUS

(TO A5 PCB*)

EXT. VGA

MONITOR

P / B

SWITCH

POT

SYSTEM

GPIB

CONNECTOR

37XXA

GPIB

CONNECTOR

PARALLEL

PORT

CONNECTOR

REAR PANEL

BIAS TEE IN

EXT. ANA

EXT. DIG

LIMIT LINE

CONNECTORS

VME BUS

TO FLOPPY

DISK DRIVE ASSY

TO EXTERNAL

KEYBOARD

* See Figure 7-2

** For future use

TO A20

FRONT PANEL PCB

TO INTERNAL

VGA MONITOR

TO A5 PCB

A18 REAR

PANEL PCB

CRT BRIGHT

DEGAUSS

A17

TO

BIAS

TEES

P/O J19**

MICROPROCESSOR

PCB

Figure 7-3. DigitalSubsystem Block Diagram