C-4 Sun Ultra 60 Service Manual • August 2001

C.1.1 UPA Interconnect

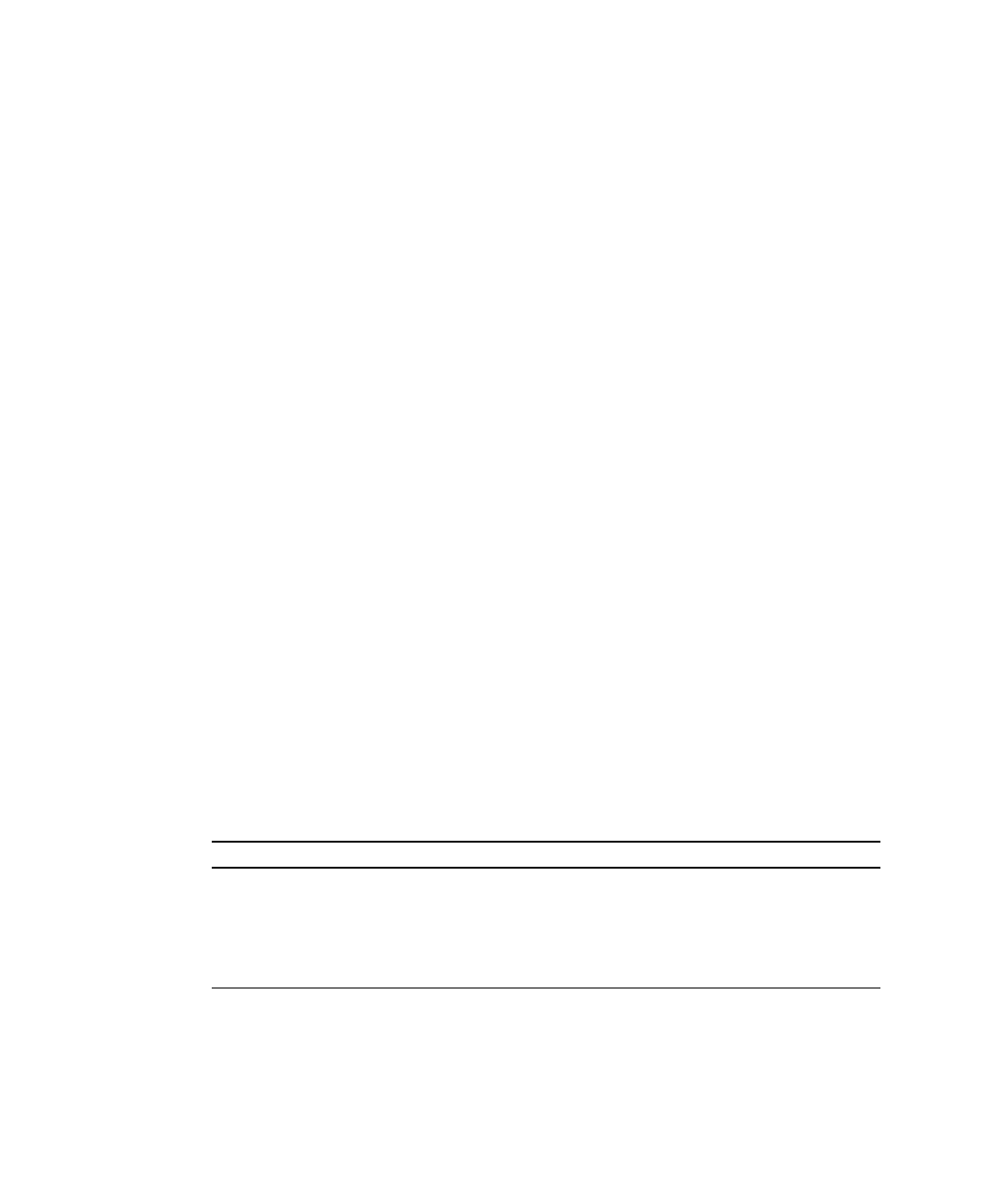

The UltraSPARC port architecture (UPA) provides a packet-based interconnect

between the UPA clients: CPU modules, PSYCHO+ ASIC, UPA graphics cards.

Electrical interconnection is provided through four address buses and four data

buses. See

FIGURE C-2.

The four address buses are:

■ UPA address bus 0 (UPA_AD0)

■ UPA address bus 1 (UPA_AD1)

■ UPA address bus 2 (UPA_AD2)

■ UPA address bus 3 (UPA_AD3)

The four data buses are:

■ UPA data bus 0 (UPA_DATA0)

■ UPA data bus 1 (UPA_DATA1)

■ UPA data bus 2 (UPA_DATA2)

■ UPA data bus 3 (UPA_DATA3)

UPA_AD0 and UPA_AD1 connect the Marvin ASIC to the CPU modules and the

PSYCHO+ ASIC. UPA_AD2 connects the Marvin ASIC to the PSYCHO+ ASIC.

UPA_AD3 connects the Marvin ASIC to the UPA graphics.

Two processor data buses (UPA_DATA0 and UPA_DATA1) are bidirectional 144-bit

data buses (128 bits of data and 16 bits of ECC). UPA_DATA0 and UPA_DATA1

connect each CPU module to the K9+ ASIC. The I/O data buses (UPA_DATA2 and

UPA_DATA3) are bidirectional data buses. UPA_DATA2 is a 64-bit data bus that

connects the PSYCHO+ ASIC and the UPA graphics. UPA_DATA3 is a 72-bit data

bus (64 bits of data and eight bits of ECC) that connects the K9+ ASIC to the

PSYCHO+ ASIC.

TABLE C-1 lists UPA port identification assignments. FIGURE C-2 illustrates how the

UPA address and data buses are connected between the UPA and the UPA clients.

TABLE C-1 UPA Port Identification Assignments

UPA Slot Number UPA Port ID <4:0>

CPU module slot 0 0x0

CPU module slot 1 0x1

PSYCHO+ ASIC 0x1F