C-14 Sun Ultra 60 Service Manual • August 2001

C.1.6.2 Memory System Timing

The Marvin ASIC generates the memory addresses and control signals to the

memory system. The UPA clock is the clock source for the Marvin ASIC and operates

as fast as 120-MHz.

C.1.7 Graphics and Imaging

The system unit takes advantage of UPA features to provide high-performance

graphics. High-performance graphics can include a vertical, single buffer UPA

graphics card or a vertical, double buffer plus Z (DBZ) UPA graphics card.

The UPA graphics card consists of the frame buffer controller (FBC) ASIC, the three-

dimensional RAM (3DRAM), the RAM digital-to-analog converter (RAMDAC), and

associated circuitry. The graphics card connects to the system unit through the

UPA64S expansion connector.

The 3DRAM is a standard dynamic random access memory (DRAM) that includes a

multi-level cache and a separate graphics port. The FBC ASIC provides acceleration

for 2D and 3D imaging primitives. This, combined with the 3DRAM cache and

support for graphics operations, supports a high-performance frame buffer.

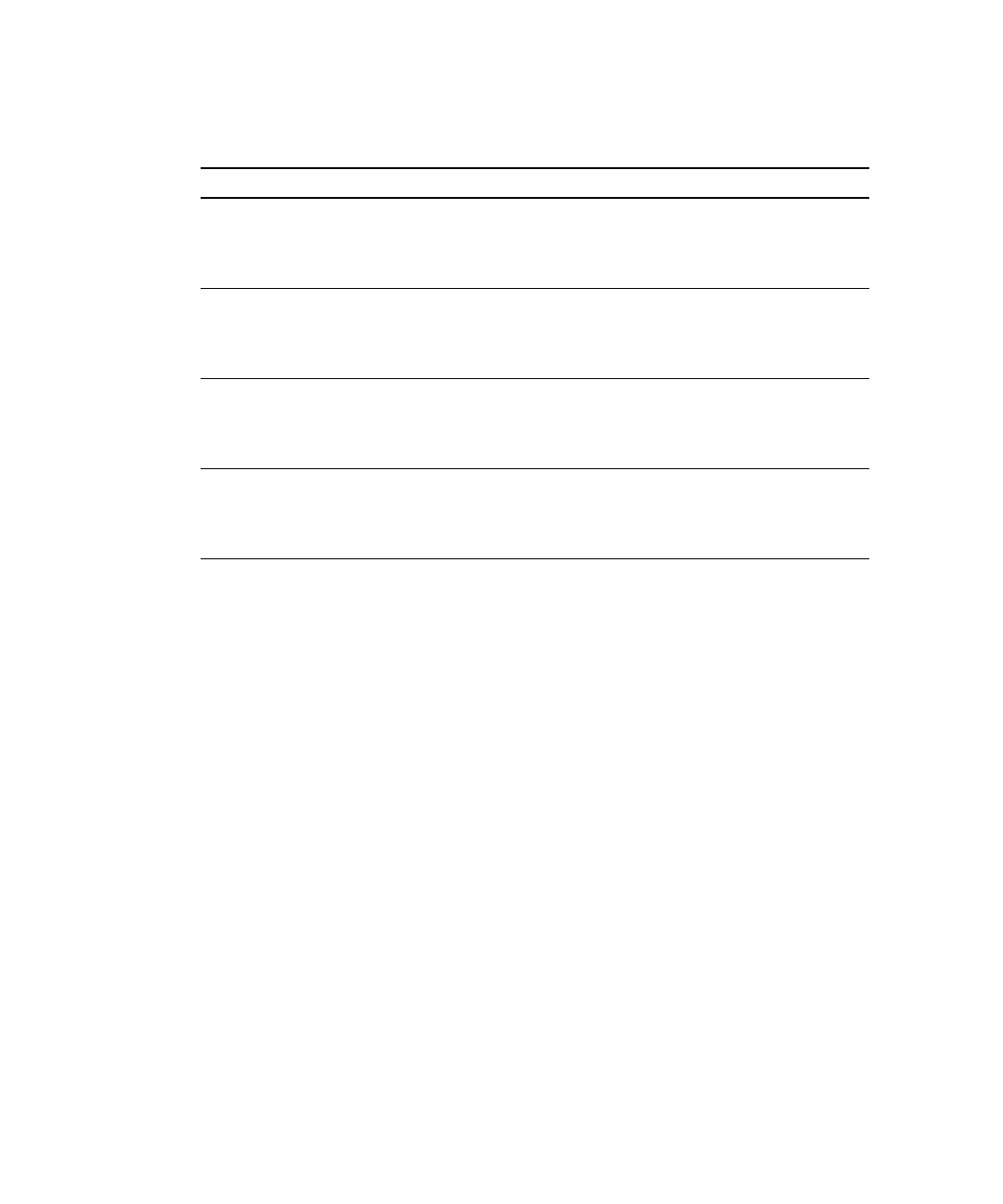

TABLE C-3 IL = 0, DIMM Bank-to-Physical Address Mapping

DIMM Bank PA[30:28]

0

0000

0001

1

0010

0011

2

1000

1001

3

1010

1011