112 AMD Geode™ SC1200/SC1201 Processor Data Book

SuperI/O Module

32579B

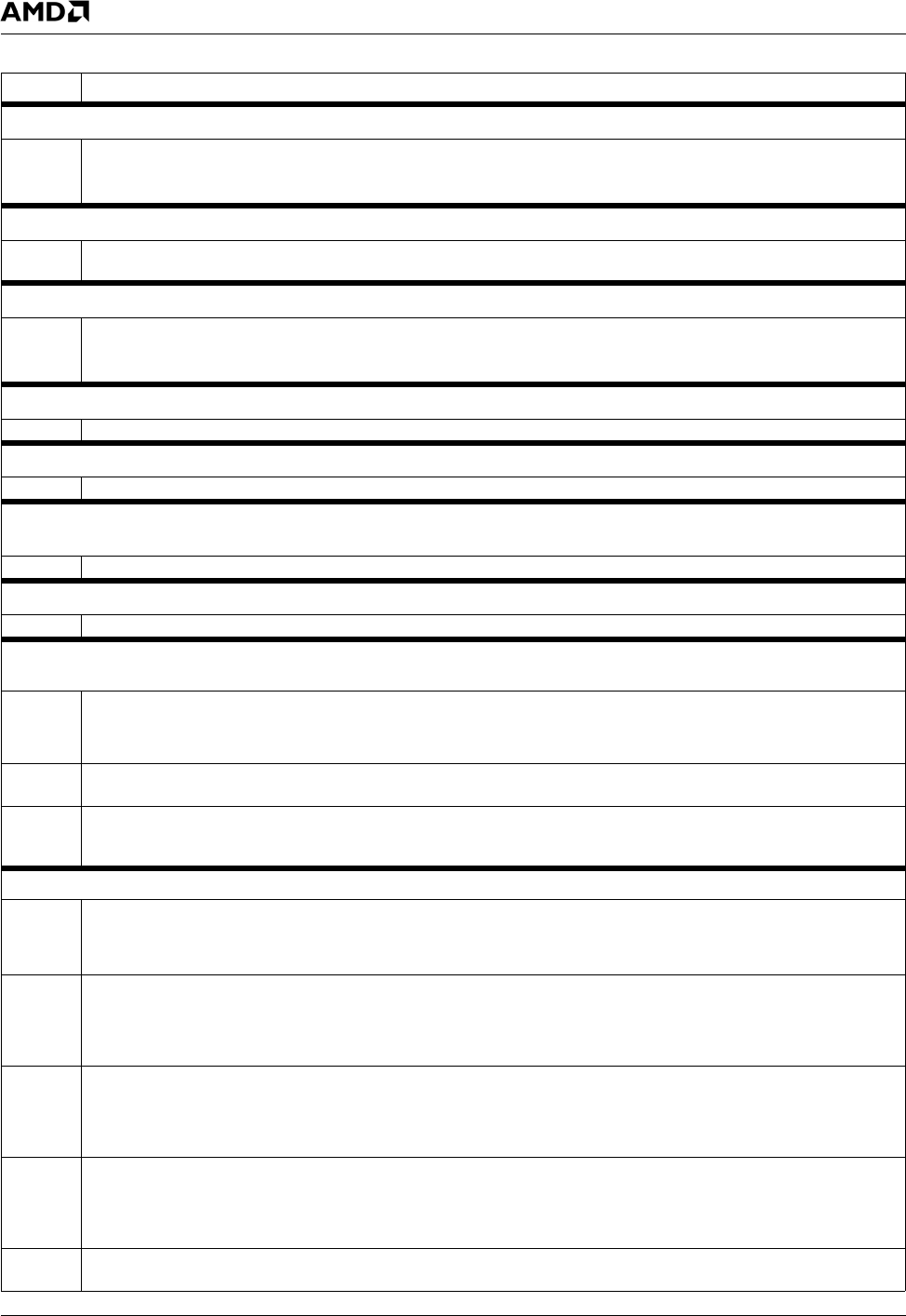

Index 03h Minutes Alarm Register - MINA (R/W) Reset Type: V

PP

PUR

7:0 Minutes Alarm Data. Values can be 00 to 59 in BCD format, or 00 to 3B in binary format.

When bits 7 and 6 are both set to 1, unconditional match is selected. See Section 5.5.2.5 "Alarms" on page 107 for more

information about “unconditional” matches.

Index 04h Hours Register - HOR (R/W) Reset Type: V

PP

PUR

7:0 Hours Data. For 12-hour mode, values can be 01 to 12 (AM) and 81 to 92 (PM) in BCD format, or 01 to 0C (AM) and 81 to

8C (PM) in binary format. For 24-hour mode, values can be 0- to 23 in BCD format or 00 to 17 in binary format.

Index 05h Hours Alarm Register - HORA (R/W) Reset Type: V

PP

PUR

7:0 Hours Alarm Data. For 12-hour mode, values may be 01 to 12 (AM) and 81 to 92 (PM) in BCD format or 01 to 0C (AM) and

81 to 8C (PM) in Binary format. For 24-hour mode, values may be 0- to 23 in BCD format or 00 to 17 in Binary format.

When bits 7 and 6 are both set to one (“11”), unconditional match is selected.

Index 06h Day of Week Register - DOW (R/W) Reset Type: V

PP

PUR

7:0 Day Of Week Data. Values may be 01 to 07 in BCD format or 01 to 07 in binary format.

Index 07h Date of Month Register - DOM (R/W) Reset Type: V

PP

PUR

7:0 Date Of Month Data. Values may be 01 to 31 in BCD format or 01 to 1F in binary format.

Index 08h Month Register - MON (R/W) Reset Type: V

PP

PUR

Width: Byte

7:0 Month Data. Values may be 01 to 12 in BCD format or 01 to 0C in binary format.

Index 09h Year Register - YER (R/W) Reset Type: V

PP

PUR

7:0 Year Data. Values may be 00 to 99 in BCD format or 00 to 63 in binary format.

Index 0Ah RTC Control Register A - CRA (R/W) Reset Type: Bit Specific

This register controls test selection, among other functions. This register cannot be written before reading bit 7 of CRD.

7 Update in Progress. (RO) This bit is not affected by reset. This bit reads 0 when bit 7 of the CRB Register is 1.

0: Timing registers not updated within 244 μs.

1: Timing registers updated within 244 μs.

6:4 Divider Chain Control. These bits control the configuration of the divider chain for timing generation and register bank

selection. See Table 5-21 on page 114. They are cleared to 000 as long as bit 7 of CRD is 0.

3:0 Periodic Interrupt Rate Select. These bits select one of fifteen output taps from the clock divider chain to control the rate of

the periodic interrupt. See Table 5-22 on page 114 and Figure 5-7 on page 106. They are cleared to 000 as long as bit 7 of

CRD is 0.

Index 0Bh RTC Control Register B - CRB (R/W) Reset Type: Bit Specific

7 Set Mode. This bit is reset at V

PP

power-up reset only.

0: Timing updates occur normally.

1: User copy of time is “frozen”, allowing the time registers to be accessed whether or not an update occurs.

6 Periodic Interrupt. Bits [3:0] of the CRA Register determine the rate at which this interrupt is generated. It is cleared to 0 on

RTC reset (i.e., hardware or software reset) or when RTC is disable.

0: Disable.

1: Enable.

5 Alarm Interrupt. This interrupt is generated immediately after a time update in which the seconds, minutes, hours, date and

month time equal their respective alarm counterparts. It is cleared to 0 as long as bit 7 of the CRD Register is reads 0.

0: Disable.

1: Enable.

4 Update Ended Interrupt. This interrupt is generated when an update occurs. It is cleared to 0 on RTC reset (i.e., hardware

or software reset) or when the RTC is disable.

0: Disable.

1: Enable.

3 Reserved. This bit is defined as “Square Wave Enable” by the MC146818 and is not supported by the RTC. This bit is

always read as 0.

Table 5-20. RTC Registers (Continued)

Bit Description