382 AMD Geode™ SC1200/SC1201 Processor Data Book

Electrical Specifications

32579B

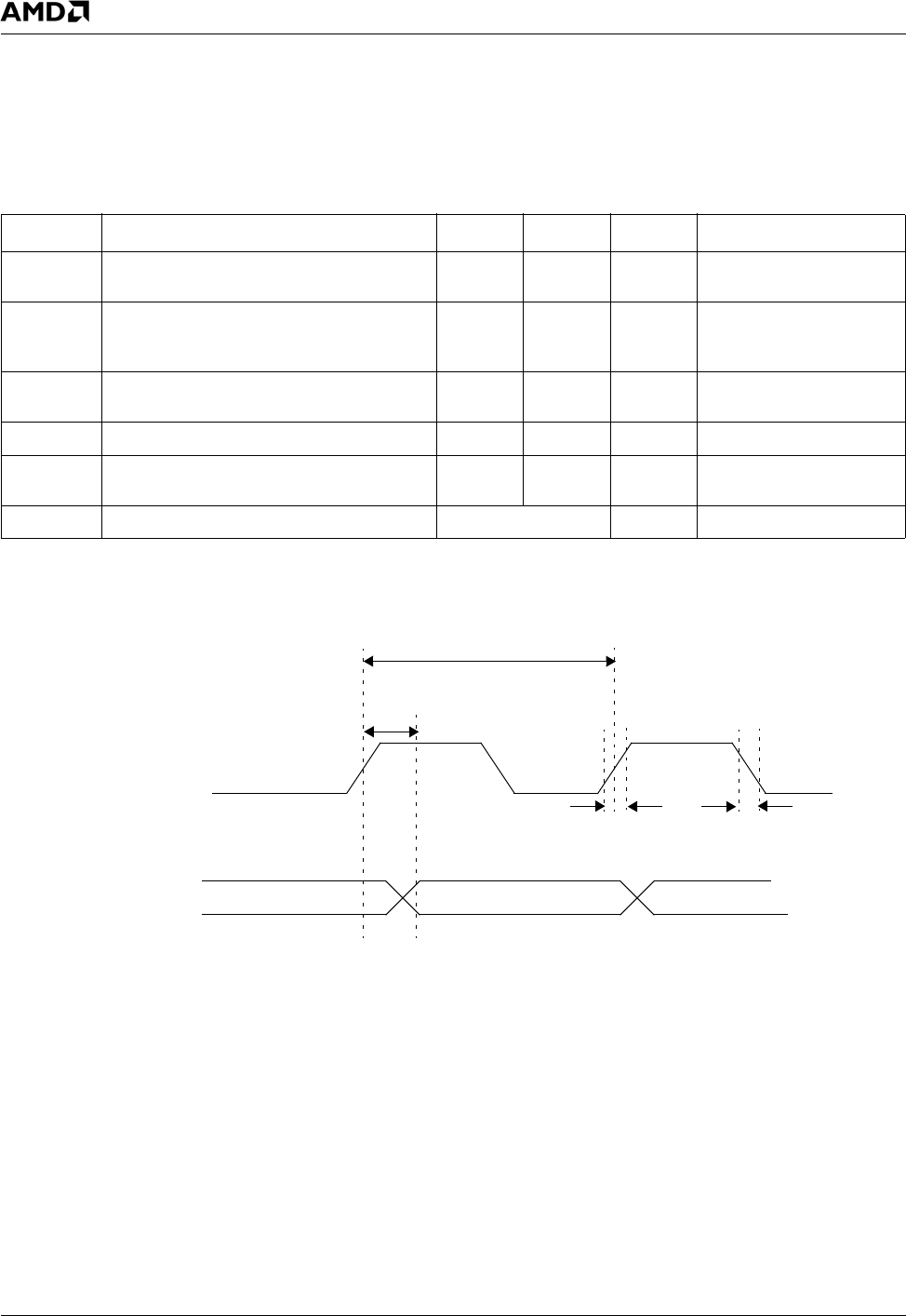

9.3.3 CRT and TFT Interface

Table 9-15 and Figure 9-8 describe the timing of the digital

CRT interface of the SC1200/SC1201 processor. All mea-

surement points in this table are identical to the voltage

measurement levels described in Table 9-11 on page 376.

Note that signals DDC_SCL and DDC_SDA of the CRT

interface are compliant with standard ACCESS.bus timing

and are controlled by software.

Figure 9-8. TFT Timing Diagram

Table 9-15. TFT Timing Parameters

Symbol Parameter Min Max Unit Comments

t

OV

TFTD[17:0], TFTDE valid time after

TFTDCK rising edge (multiplexed on IDE)

08ns

t

OV

TFTD[17:0], TFTDE valid time after

TFTDCK rising edge (multiplexed on

Parallel Port)

04ns

t

CLK_RF

TFTDCK rise/fall time between 0.8V and

2.0V

3 ns Note 1

t

CLK_P

TFTDCK period time (multiplexed on IDE) 25 ns

t

CLK_P

TFTDCK period time (multiplexed on

Parallel Port)

12.5 ns

t

CLK_D

TFTDCK duty cycle 40/60 %

Note 1. Guaranteed by characterization.

t

OV

t

CLK_RF

t

CLK_P

TFTDCK

TFTD[17:0]

TFTDE