216 AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

32579B

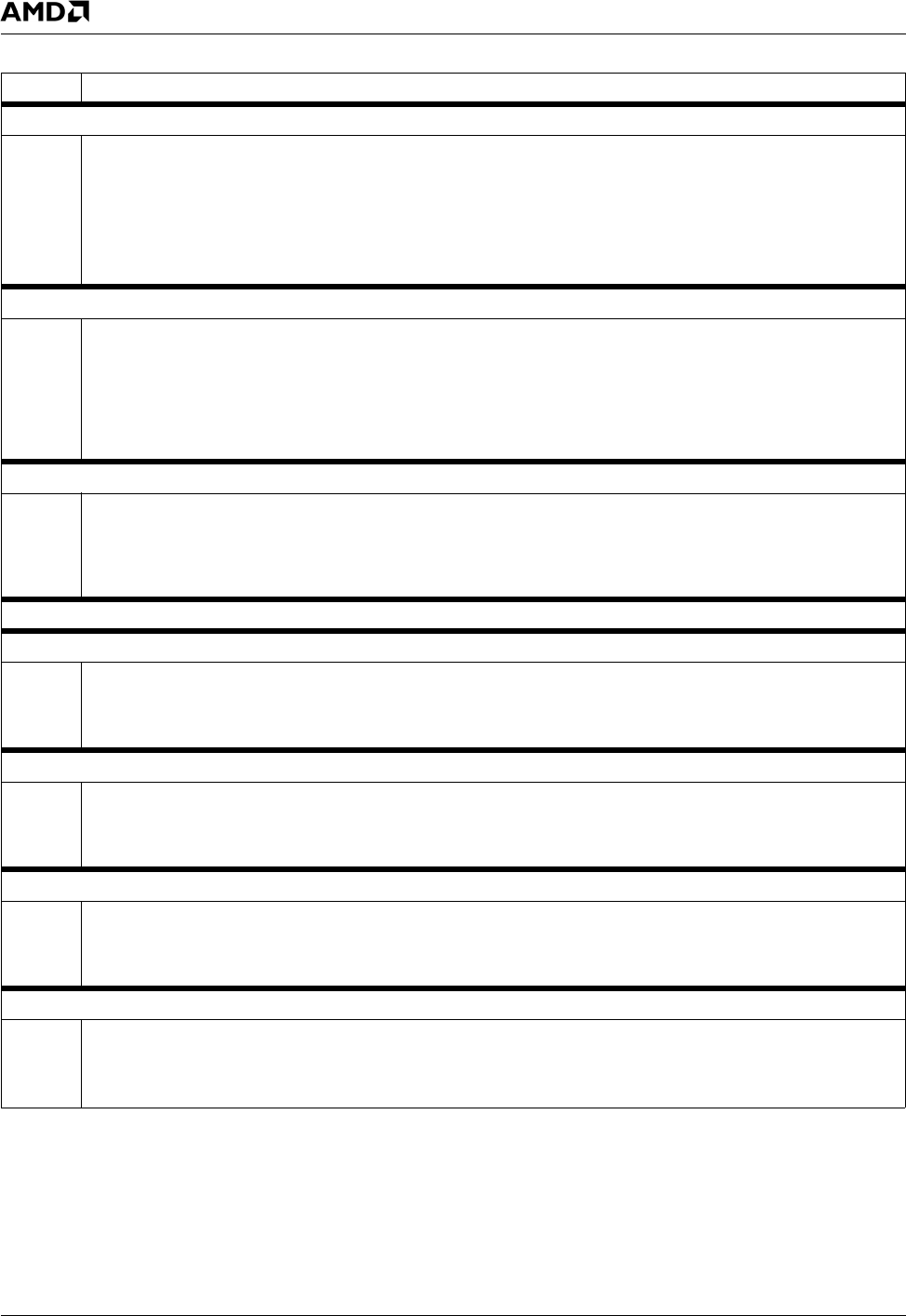

Index ACh-ADh Secondary Hard Disk Idle Timer Count Register (R/W) Reset Value: 0000h

15:0 Secondary Hard Disk Idle Timer Count. This idle timer is used to determine when the secondary hard disk is not in use so

that it can be powered down. The 16-bit value programmed in this register represents the period of hard disk inactivity after

which the system is alerted via an SMI. The timer is automatically reloaded with the count value whenever an access occurs

to the configured hard disk’s data port (I/O port 1F0h or 170h).

This counter uses a 1 second timebase. To enable this timer, set F0 Index 83h[7] = 1.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 86h/F6h[4].

Index AEh CPU Suspend Command Register (WO) Reset Value: 00h

7:0 Software CPU Suspend Command. If bit 0 in the Clock Stop Control register is set low (F0 Index BCh[0] = 0), a write to

this register causes an internal SUSP#/SUSPA# handshake with the GX1 module, placing the GX1 module in a low-power

state. The actual data written is irrelevant. Once in this state, any unmasked IRQ or SMI releases the GX1 module halt con-

dition.

If F0 Index BCh[0] = 1, writing to this register invokes a full system Suspend. In this case, the internal SUSP_3V signal is

asserted after the SUSP#/SUSPA# halt. Upon a Resume event, the PLL delay programmed in the F0 Index BCh[7:4] is

invoked, allowing the clock chip and GX1 module PLL to stabilize before de-asserting SUSP#.

Index AFh Suspend Notebook Command Register (WO) Reset Value: 00h

7:0 Software CPU Stop Clock Suspend. A write to this register causes a SUSP#/SUSPA# handshake with the CPU, placing

the GX1 module in a low-power state. Following this handshake, the SUSP_3V signal is asserted. The SUSP_3V signal is

intended to be used to stop all system clocks.

Upon a Resume event, the internal SUSP_3V signal is de-asserted. After a slight delay, the Core Logic module de-asserts

the SUSP# signal. Once the clocks are stable, the GX1 module de-asserts SUSPA# and system operation resumes.

Index B0h-B3h Reserved Reset Value: 00h

Index B4h Floppy Port 3F2h Shadow Register (RO) Reset Value: xxh

7:0 Floppy Port 3F2h Shadow. Last written value of I/O Port 3F2h. Required for support of FDC power On/Off and 0V Sus-

pend/Resume coherency.

This register is a copy of an I/O register which cannot safely be directly read. The value in this register is not deterministic of

when the register is being read. It is provided here to assist in a Suspend-to-Disk operation.

Index B5h Floppy Port 3F7h Shadow Register (RO) Reset Value: xxh

7:0 Floppy Port 3F7h Shadow. Last written value of I/O Port 3F7h. Required for support of FDC power On/Off and 0V Sus-

pend/Resume coherency.

This register is a copy of an I/O register which cannot safely be directly read. The value in this register is not deterministic of

when the register is being read. It is provided here to assist in a Suspend-to-Disk operation.

Index B6h Floppy Port 372h Shadow Register (RO) Reset Value: xxh

7:0 Floppy Port 372h Shadow. Last written value of I/O Port 372h. Required for support of FDC power On/Off and 0V Sus-

pend/Resume coherency.

This register is a copy of an I/O register which cannot safely be directly read. The value in this register is not deterministic of

when the register is being read. It is provided here to assist in a Suspend-to-Disk operation.

Index B7h Floppy Port 377h Shadow Register (RO) Reset Value: xxh

7:0 Floppy Port 377h Shadow. Last written value of I/O Port 377h. Required for support of FDC power On/Off and 0V Sus-

pend/Resume coherency.

This register is a copy of an I/O register which cannot safely be directly read. The value in this register is not deterministic of

when the register is being read. It is provided here to assist in a Suspend-to-Disk operation.

Table 6-29. F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support (Continued)

Bit Description