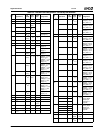

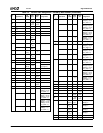

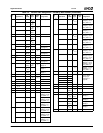

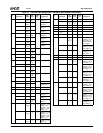

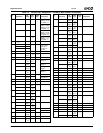

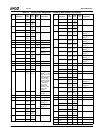

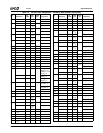

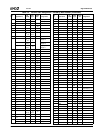

AMD Geode™ SC1200/SC1201 Processor Data Book 31

Signal Definitions

32579B

C1 AD26 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D2 I/O IN

PCI

,

O

PCI

C2 AD24 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D0 I/O IN

PCI

,

O

PCI

C3 V

IO

PWR --- --- ---

C4 AD25 I/O IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

D1 I/O IN

PCI

,

O

PCI

C5 GNT0# O O

PCI

V

IO

---

DID0 I

(PD

100

)

IN

STRP

Strap (See Table 3-

4 on page 44.)

C6 GNT1# O O

PCI

V

IO

---

DID1 I

(PD

100

)

IN

STRP

Strap (See Table 3-

4 on page 44.)

C7 V

IO

PWR --- --- ---

C8 ROMCS# O O

3/5

V

IO

---

BOOT16 I

(PD

100

)

IN

STRP

V

IO

Strap (See Table 3-

4 on page 44.)

C9 GPIO19 I/O

(PU

22.5

)

IN

TS

,

O

3/5

V

IO

PMR[9] = 0 and

PMR[4] = 0

INTC# I

(PU

22.5

)

IN

TS

PMR[9] = 0 and

PMR[4] = 1

IOCHRDY I

(PU

22.5

)

IN

TS1

PMR[9] = 1 and

PMR[4] = 1

C10 V

IO

PWR --- --- ---

C11 IRTX O O

8/8

V

IO

PMR[6] = 0

SOUT3 O O

8/8

PMR[6] = 1

C12 V

SSCRT

GND --- --- ---

C13 AV

CCCRT

PWR --- --- ---

C14 AV

SSCRT

GND --- --- ---

C15 AV

SSCRT

GND --- --- ---

C16 AV

SSPLL2

GND --- --- ---

C17

6,2

SLCT I IN

T

V

IO

PMR[23]

3

= 0 and

(PMR[27] = 0 and

FPCI_MON = 0)

TFTD15 O O

1/4

PMR[23]

3

= 1 and

(PMR[27] = 0 and

FPCI_MON = 0)

F_C/BE3# O O

1/4

PMR[23]

3

= 0 and

(PMR[27] = 1 or

FPCI_MON = 1)

C18 PD4 I/O IN

T

,

O

14/14

V

IO

PMR[23]

3

= 0 and

(PMR[27] = 0 and

FPCI_MON = 0)

TFTD10 O O

1/4

PMR[23]

3

= 1 and

(PMR[27] = 0 and

FPCI_MON = 0)

F_AD4 O O

14/14

PMR[23]

3

= 0 and

(PMR[27] = 1 or

FPCI_MON = 1)

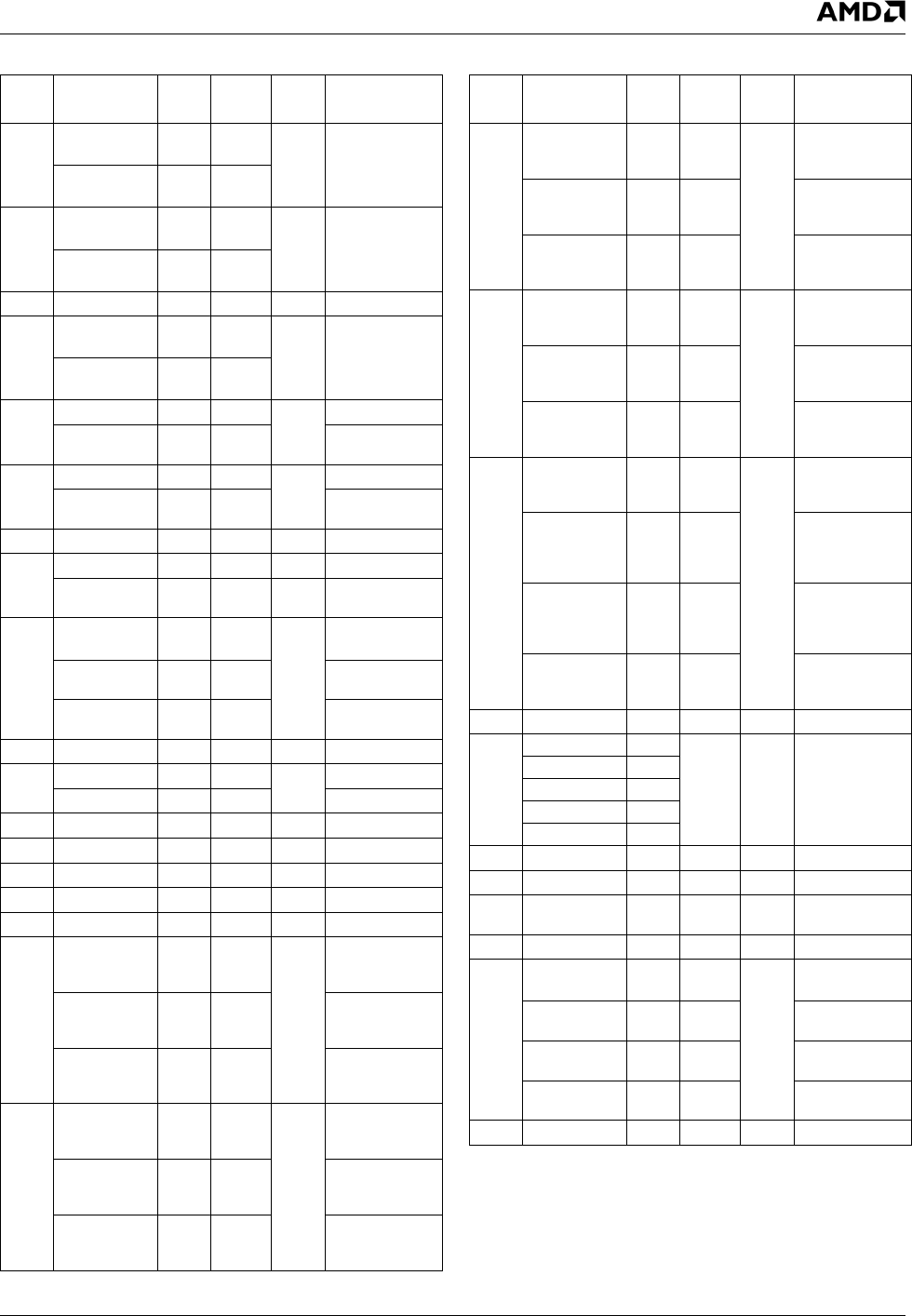

Ball

No. Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail Configuration

C19

6,2

PD5 I/O IN

T

,

O

14/14

V

IO

PMR[23]

3

= 0 and

(PMR[27] = 0 and

FPCI_MON = 0)

TFTD11 O O

1/4

PMR[23]

3

= 1 and

(PMR[27] = 0 and

FPCI_MON = 0)

F_AD5 O O

14/14

PMR[23]

3

= 0 and

(PMR[27] = 1 or

FPCI_MON = 1)

C20

6,2

PD3 I/O IN

T

,

O

14/14

V

IO

PMR[23]

3

= 0 and

(PMR[27] = 0 and

FPCI_MON = 0)

TFTD9 O O

1/4

PMR[23]

3

= 1 and

(PMR[27] = 0 and

FPCI_MON = 0)

F_AD3 O O

14/14

PMR[23]

3

= 0 and

(PMR[27] = 1 or

FPCI_MON = 1)

C21

6,2

PD0 I/O IN

T

,

O

14/14

V

IO

PMR[23]

3

= 0 and

(PMR[27] = 0 and

FPCI_MON = 0)

TFTD6 O O

1/4

(PMR[23]

3

= 1 and

PMR[15] = 0) and

(PMR[27] = 0 and

FPCI_MON = 0)

VOPD5 O O

1/4

(PMR[23]

3

= 1 and

PMR[15] = 1) and

(PMR[27] = 0 and

FPCI_MON = 0)

F_AD0 O O

14/14

PMR[23]

3

= 0 and

(PMR[27] = 1 or

FPCI_MON = 1)

C22 V

IO

PWR --- --- ---

C23 SVC O WIRE AV

CCTV

See F4BAR0+

Memory Offset

C08h[4:3] bit

description on

page 356.

Cr O

Cb O

TVB O

TVR O

C24 TVREF I/O WIRE AV

CCTV

---

C25 V

IO

PWR --- --- ---

C26 INTB# I

(PU

22.5

)

IN

PCI

V

IO

---

C27 AV

SSUSB

GND --- --- ---

C28 GPIO9 I/O

(PU

22.5

)

IN

TS

,

O

1/4

V

IO

PMR[18] = 0 and

PMR[8] = 0

DCD2# I

(PU

22.5

)

IN

TS

PMR[18] = 1 and

PMR[8] = 0

IDE_IOW1# O

(PU

22.5

)

O

1/4

PMR[18] = 0 and

PMR[8] = 1

SDTEST2 O

(PU

22.5

)

O

2/5

PMR[18] = 1 and

PMR[8] = 1

C29 V

IO

PWR --- --- ---

Ball

No. Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail Configuration

Table 3-2. BGU481 Ball Assignment - Sorted by Ball Number (Continued)