AMD Geode™ SC1200/SC1201 Processor Data Book 411

Electrical Specifications

32579B

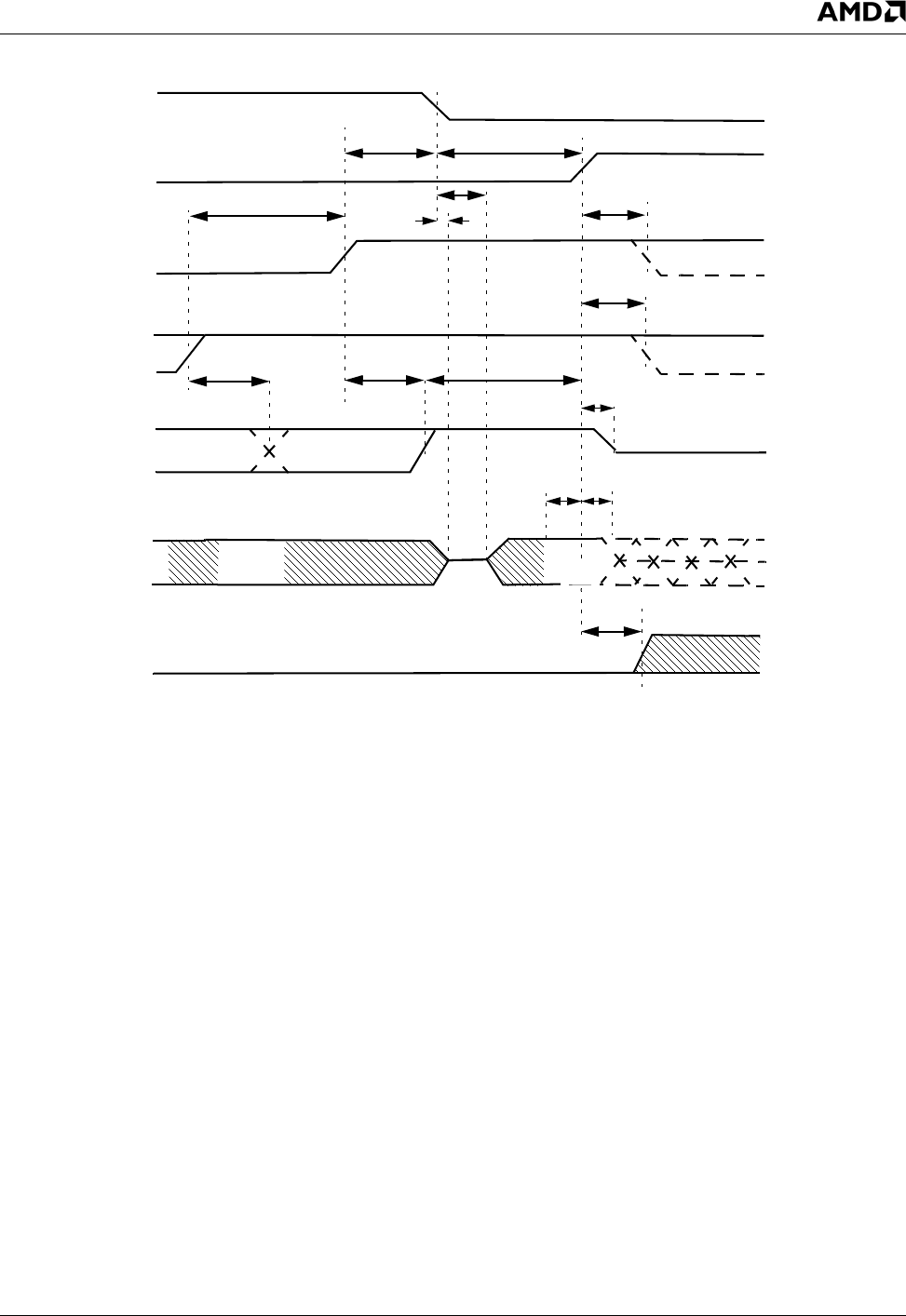

Figure 9-32. Host Terminating an UltraDMA Data In Burst Timing Diagram

IDE_DATA[15:0]

(device)

IDE_CS[0:1]#

IDE_ADDR[2:0]

CR

t

ACK

t

DVH

t

DVS

t

ACK

t

IORDYZ

t

ACK

t

MLI

t

LI

t

RP

t

MLI

t

LI

t

RFS

t

AZ

t

ZAH

IDE_IRDY0

(DSTROBE0)

(device)

IDE_IOR0#

(HDMARDY0#)

(host)

IDE_IOW0#

(STOP0#)

(host)

IDE_DACK0#

(host)

IDE_DREQ0

(device)

Note: The definitions for the IDE_IOW[0:1]# (STOP[0:1]#), IDE_IOR[0:1]# (HDMARDY[0:1]#), and IDE_IRDY[0:1]

(DSTROBE[0:1]) signal lines are no longer in effect after IDE_DREQ[0:1] and IDE_DACK[0:1] are de-asserted.