AMD Geode™ SC1200/SC1201 Processor Data Book 355

Video Processor Module - Video Processor Registers - Function 4

32579B

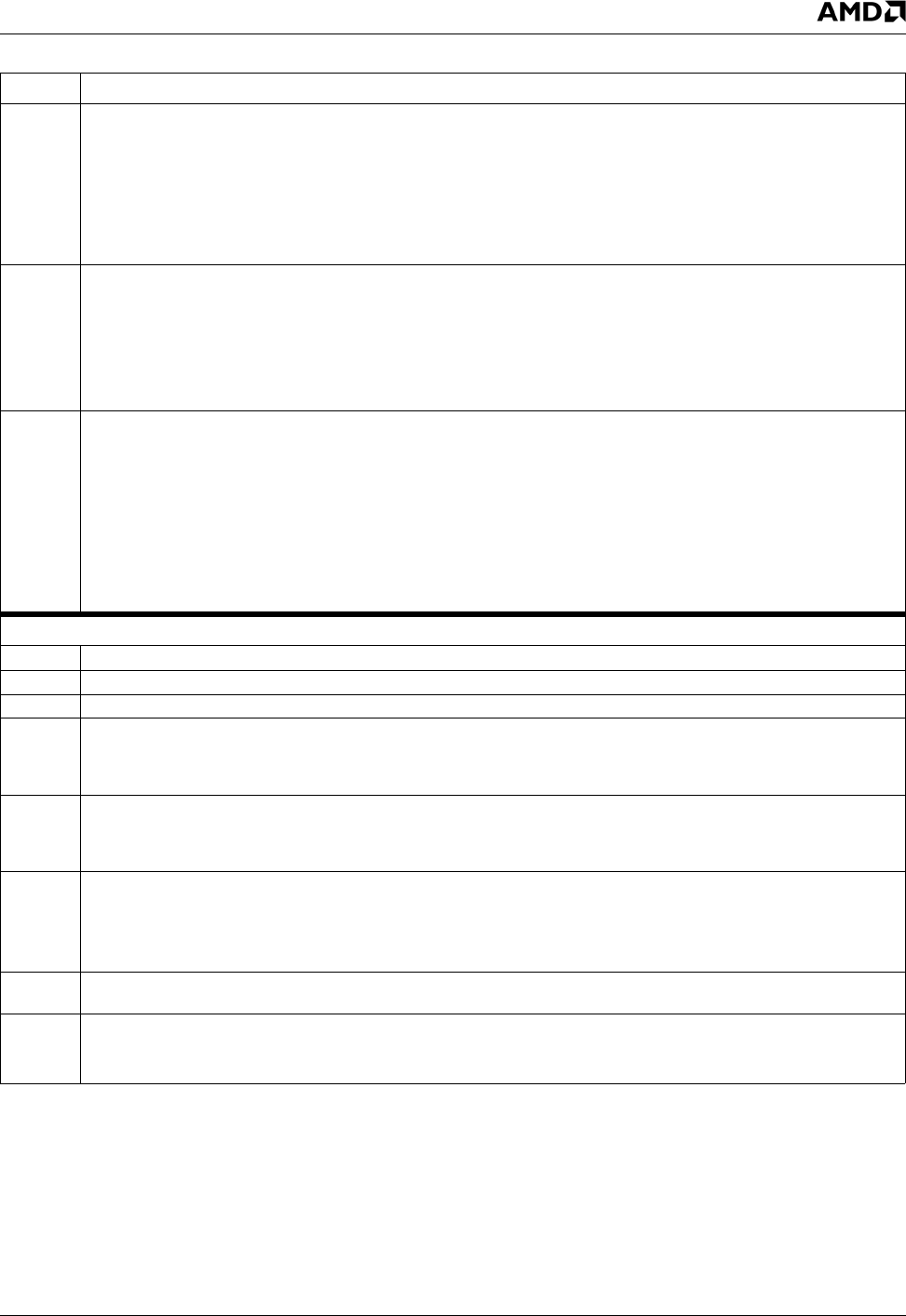

22:21 REFEN[1:0] (Enable FrameRef). Enables the externally provided FrameRef to initialize the horizontal and vertical counters

and/or the internal frame counter.

00: No initialization.

01: The horizontal and vertical counters are initialized to the values in HPhase and VPhase.

10: The internal frame counter is set to 3.

11: The horizontal and vertical counters are initialized to the values in HPhase and VPhase and the internal frame counter

is set to 3,

20:11 VPHASE (Vertical Phase). Defines the phase (i.e., the number of lines) between the internal vertical counter and the exter-

nally provided FrameRef.

If REFEN[0] (bit 21) = 1, the vertical counter in the video timing generator is set to this value when FrameRef is asserted.

Valid values are:

PAL: 1 to 625

NTSC: 1 to 525

10:0 HPHASE. (Horizontal Phase). This bit field defines the phase (i.e., the number of pixels) between the internal horizontal

counter and an externally provided FrameRef.

If REFEN[0] (bit 21) = 1, the horizontal counter in the video generator is set to this value when FrameRef is asserted.

The counter is split into two parts, a 10-bit “half-line” counter and a single bit “line-half”. The half-line counter counts half a

line and is reset. When the half-line counter is reset, the line-half indicator toggles.

In PAL mode, there are 1728 27 MHz clock cycles per line. In this mode, the half-line counter counts 0 to 863. To set the hor-

izontal phase to a value HP between 0 and 1727, HPHASE[10] is set to HP/864 and HPHASE[9:0] is set to HP%864.

In NTSC mode, there are 1716 27 MHz clock cycles per line, so HPHASE[10] is set to HP/858 and HPHASE[9:0] is set to

HP%858.

Offset C04h-C07h Timing & Encoder Control 2 Register Reset Value: 1FF00000h

31 Anlg (Analog Line). When set, the horizontal blanking interval is increased to comply with relevant specification.

30 TV DAC Mode Bit 2. See TV DAC Mode Bits [1:0] (F4BAR0+Memory Offset C08h[4:3]).

29:20 Reserved.

19 Y2BP (Luminance Bypass). Luminance 2x oversampling bypass.

0: Disable.

1: Enable.

18 C2BP (Chrominance Bypass). Chrominance 2x oversampling bypass.

0: Disable.

1: Enable.

17:16 CFS (Chrominance Lowpass Filter Select). Selects one of three frequency responses for the chrominance lowpass filter:

00 or 01: Filter is bypassed.

10: 1.3 MHz lowpass for composite video output.

11: 1.8 MHz lowpass for S-Video output.

15:8 HUE (Hue Offset). Defines a fixed hue offset which is added to the subcarrier phase during the active video portion of the

line. The value programmed is: hue (degrees) / 256.

7:0 SCPHASE (Subcarrier Phase). Defines the subcarrier phase at the start of a two-frame sequence (NTSC) or four-frame

sequence (PAL).

The number is: phase (in degrees) / 256.

Table 7-9. F4BAR0+Memory Offset: Video Processor Configuration Registers (Continued)

Bit Description