AMD Geode™ SC1200/SC1201 Processor Data Book 167

Core Logic Module

32579B

6.2.11 GPIO Interface

Up to 64 GPIOs in the in the Core Logic module are pro-

vided for system control. For further information, see Sec-

tion 4.2 "Pin Multiplexing, Interrupt Selection, and Base

Address Registers" on page 72 and Table 6-30 "F0BAR0+I/

O Offset: GPIO Configuration Registers" on page 224.

Note: Not all GPIOs are available on SC1200/SC1201

processor balls. GPIOs [63:42], [31:21], and [5:2]

are reserved.

6.2.12 Integrated Audio

The Core Logic module provides hardware support for the

Virtual (soft) Audio subsystem as part of the Virtual System

Architecture™ (VSA) technology for capture and playback

of audio using an external codec. This eliminates much of

the hardware traditionally associated with audio functions.

This hardware support includes:

• Six-channel buffered PCI bus mastering interface.

• AC97 version 2.0 compatible interface to the codec. Any

codec, which supports an independent input and output

sample rate conversion interface, can be used with the

Core Logic module.

Additional hardware provides the necessary functionality

for VSA. This hardware includes the ability to:

• Generate an SMI to alert software to update required

data. An SMI is generated when either audio buffer is

half empty or full. If the buffers become completely

empty or full, the Empty bit is asserted.

• Generate an SMI on I/O traps.

• Trap accesses for sound card compatibility at either I/O

Port 220h-22Fh, 240h-24Fh, 260h-26Fh, or 280h-28Fh.

• Trap accesses for FM compatibility at I/O Port 388h-

38Bh.

• Trap accesses for MIDI UART interface at I/O Port 300h-

301h or 330h-331h.

• Trap accesses for serial input and output at COM2 (I/O

Port 2F8h-2FFh) or COM4 (I/O Port 2E8h-2EFh).

• Support trapping for low (I/O Port 00h-0Fh) and/or high

(I/O Port C0h-DFh) DMA accesses.

• Support hardware status register reads in Core Logic

module, minimizing SMI overhead.

• Support is provided for software-generated IRQs on IRQ

2, 3, 5, 7, 10, 11, 12, 13, 14, and 15.

The following subsections include details of the registers

used for configuring the audio interface. The registers are

accessed through F3 Index 10h, the Base Address Regis-

ter (F3BAR0) in Function 3. F3BAR0 sets the base

address for the audio support registers as shown in Table

6-37 "F3: PCI Header Registers for Audio Configuration"

on page 262.

6.2.12.1 Data Transport Hardware

The data transport hardware can be broadly divided into

two sections: bus mastering and the codec interface.

Audio Bus Masters

The Core Logic module audio hardware includes six PCI

bus masters (three for input and three for output) for trans-

ferring digitized audio between memory and the external

codec. With these bus master engines, the Core Logic

module off-loads the CPU and improves system perfor-

mance.

The programming interface defines a simple scatter/gather

mechanism allowing large transfer blocks to be scattered to

or gathered from memory. This cuts down on the number of

interrupts to and interactions with the CPU.

The six bus masters that directly drive specific slots on the

AC97 interface are described in Table 6-10.

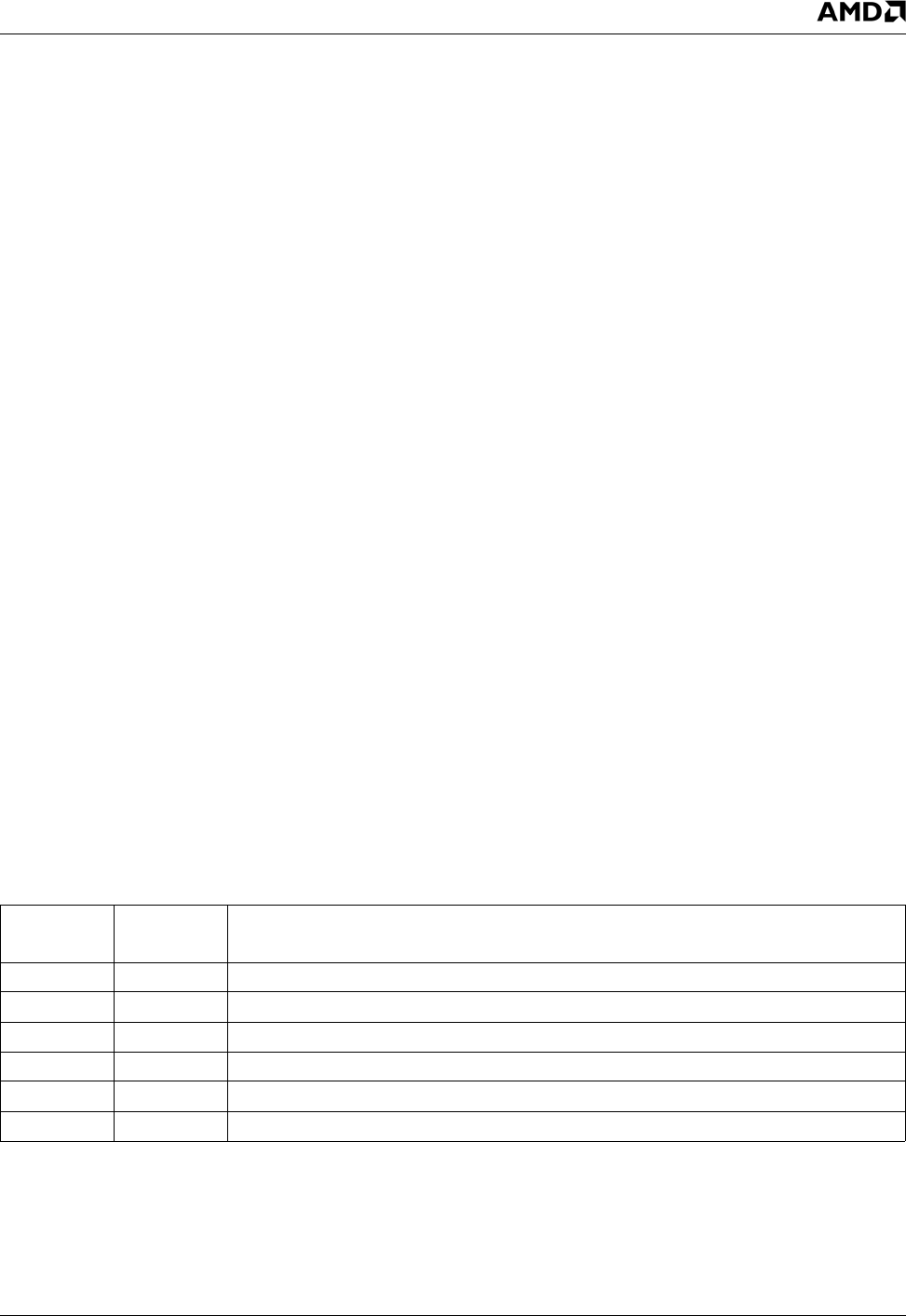

Table 6-10. Bus Masters That Drive Specific Slots of the AC97 Interface

Audio Bus

Master # Slots Description

0 3 and 4 32-Bit output to codec. Left and right channels.

1 3 and 4 32-Bit input from codec. Left and right channels.

2 5 16-Bit output to codec.

3 5 16-Bit input from codec.

4 6 or 11 16-Bit output to codec. Slot in use is determined by F3BAR0+Memory Offset 08h[19].

5 6 or 11 16-Bit input from codec. Slot in use is determined by F3BAR0+Memory Offset 08h[20].