304 AMD Geode™ SC1200/SC1201 Processor Data Book

Core Logic Module - ISA Legacy Register Space

32579B

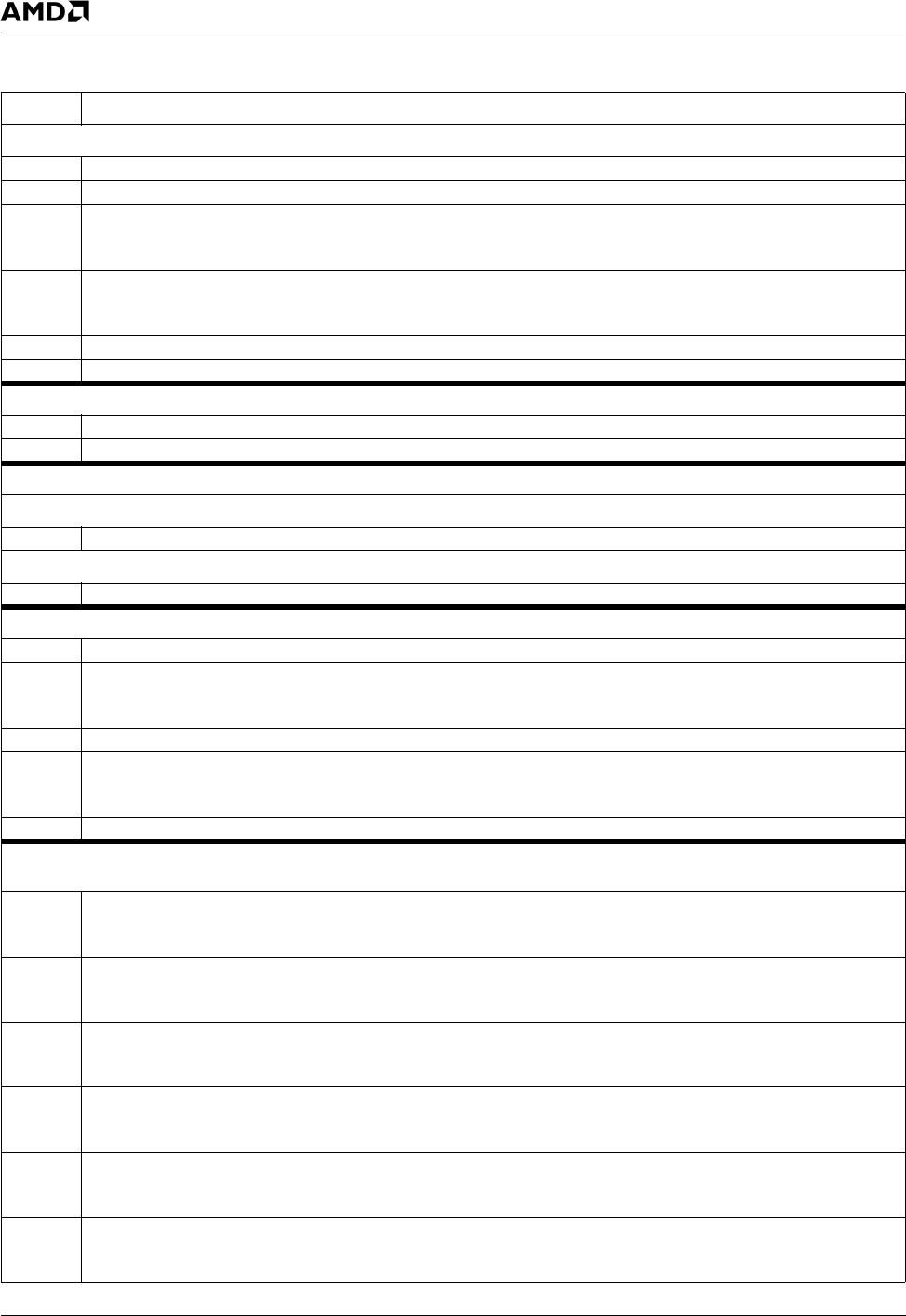

Table 6-46. Programmable Interrupt Controller Registers

Bit Description

I/O Port 020h / 0A0h Master / Slave PIC ICW1 (WO)

7:5 Reserved. Must be set to 0.

4 Reserved. Must be set to 1.

3 Trigger Mode.

0: Edge.

1: Level.

2 Vector Address Interval

0: 8 byte intervals.

1: 4 byte intervals.

1 Reserved. Must be set to 0 (cascade mode).

0 Reserved. Must be set to 1 (ICW4 must be programmed).

I/O Port 021h / 0A1h Master / Slave PIC ICW2 (after ICW1 is written) (WO)

7:3 A[7:3]. Address lines [7:3] for base vector for interrupt controller.

2:0 Reserved. Must be set to 0.

I/O Port 021h / 0A1h Master / Slave PIC ICW3 (after ICW2 is written) (WO)

Master PIC ICW3

7:0 Cascade IRQ. Must be 04h.

Slave PIC ICW3

7:0 Slave ID. Must be 02h.

I/O Port 021h / 0A1h Master / Slave PIC ICW4 (after ICW3 is written) (WO)

7:5 Reserved. Must be set to 0.

4 Special Fully Nested Mode.

0: Disable.

1: Enable.

3:2 Reserved. Must be set to 0.

1 Auto EOI.

0: Normal EOI.

1: Auto EOI.

0 Reserved. Must be set to 1 (8086/8088 mode).

I/O Port 021h / 0A1h (R/W) Master / Slave PIC OCW1

(except immediately after ICW1 is written)

7 IRQ7 / IRQ15 Mask.

0: Not Masked.

1: Mask.

6 IRQ6 / IRQ14 Mask.

0: Not Masked.

1: Mask.

5 IRQ5 / IRQ13 Mask.

0: Not Masked.

1: Mask.

4 IRQ4 / IRQ12 Mask.

0: Not Masked.

1: Mask.

3 IRQ3 / IRQ11 Mask.

0: Not Masked.

1: Mask.

2 IRQ2 / IRQ10 Mask.

0: Not Masked.

1: Mask.