AMD Geode™ SC1200/SC1201 Processor Data Book 169

Core Logic Module

32579B

4) Read the SMI Status register to clear the Bus Master

Error and End of Page bits (bits 1 and 0).

Set the correct direction to the Read or Write Control

bit (Command register bit 3). Note that the direction of

the data transfer of a particular bus master is fixed and

therefore the direction bit must be programmed

accordingly. It is assumed that the codec has been

properly programmed to receive the audio data.

Engage the bus master by writing a “1” to the Bus

Master Control bit (Command register bit 0).

The bus master reads the PRD entry pointed to by the

PRD Table Address register and increments the

address by 08h to point to the next PRD. The transfer

begins.

Example - The bus master is now properly pro-

grammed to transfer Audio Buffer_1 to a specific

slot(s) in the AC97 interface.

5) The bus master transfers data to/from memory

responding to bus master requests from the AC97

interface. At the completion of each PRD, the bus mas-

ter’s next response depends on the settings of the

flags in the PRD.

Example - At the completion of PRD_1 an SMI is gen-

erated because the EOP bit is set while the bus mas-

ter continues on to PRD_2. The address in the PRD

Table Address register is incremented by 08h and is

now pointing to PRD_3. The SMI Status register is

read to clear the End of Page status flag. Since Audio

Buffer_1 is now empty, the software can refill it.

At the completion of PRD_2 an SMI is generated

because the EOP bit is set. The bus master then con-

tinues on to PRD_3. The address in the PRD Table

Address register is incremented by 08h. The DMA SMI

Status register is read to clear the End of Page status

flag. Since Audio Buffer_2 is now empty, the software

can refill it. Audio Buffer_1 has been refilled from the

previous SMI.

PRD_3 has the JMP bit set. This means the bus mas-

ter uses the address stored in PRD_3 (Address_3) to

locate the next PRD. It does not use the address in the

PRD Table Address register to get the next PRD. Since

Address_3 is the location of PRD_1, the bus master

has looped the PRD table.

Stopping the bus master can be accomplished by not read-

ing the SMI Status register End of Page status flag. This

leads to a second EOP which causes a Bus Master Error

and pauses the bus master. In effect, once a bus master

has been enabled it never has to be disabled, just paused.

The bus master cannot be disabled unless the bus master

has been paused or has reached an EOT.

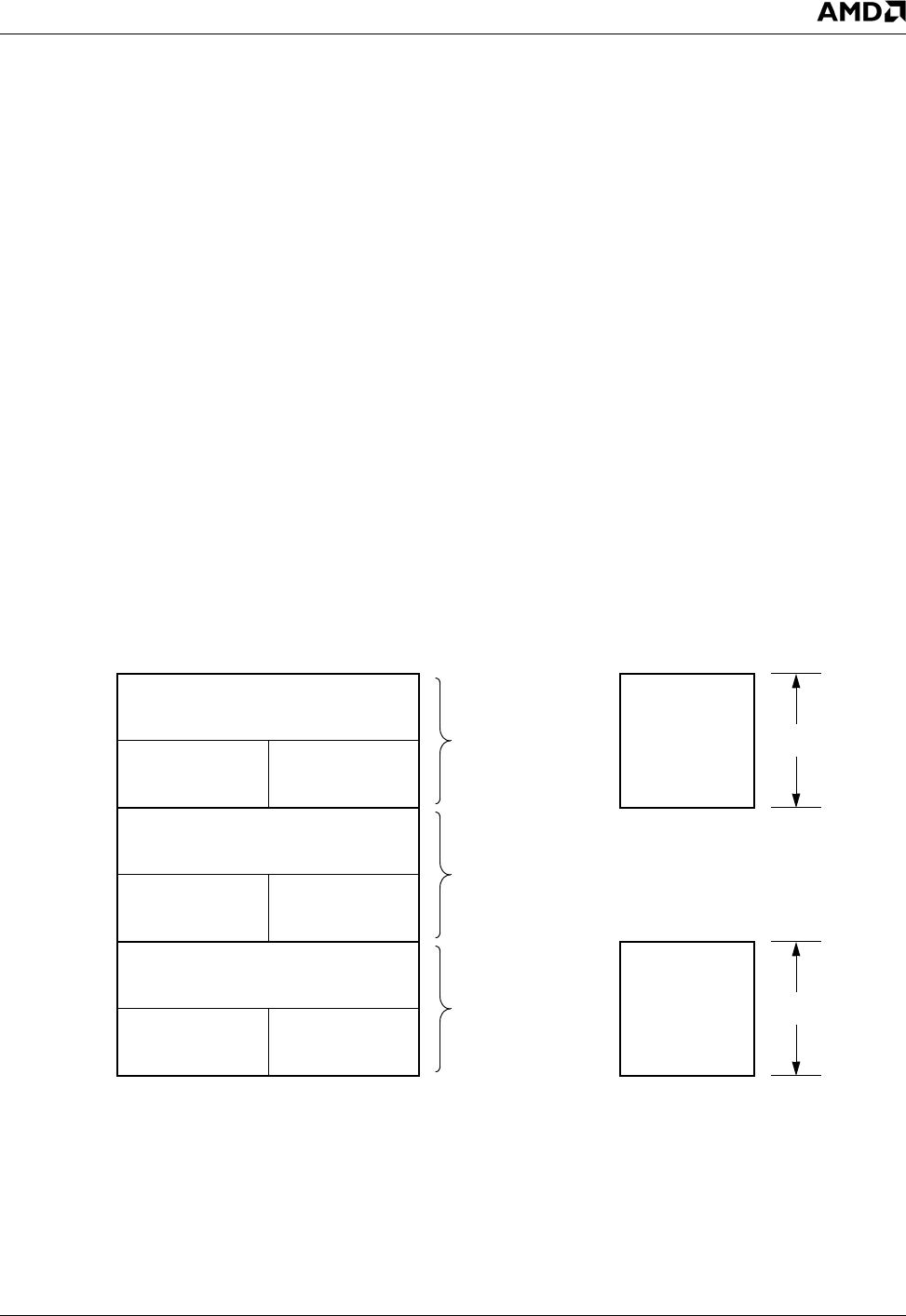

Figure 6-12. PRD Table Example

Address_1

Size_1

EOT = 0

Audio

Buffer_1

Audio

Buffer_2

Size_1

Size_2

Address_1

EOP = 1

JMP = 0

Address_2

Size_2

EOT = 0

EOP = 1

JMP = 0

Address_3

Don’t Care

EOT = 0

EOP = 0

JMP = 1

PRD_1

PRD_2

PRD_3

Address_2

Address_3

32-byte

boundary