AMD Geode™ SC1200/SC1201 Processor Data Book 57

Signal Definitions

32579B

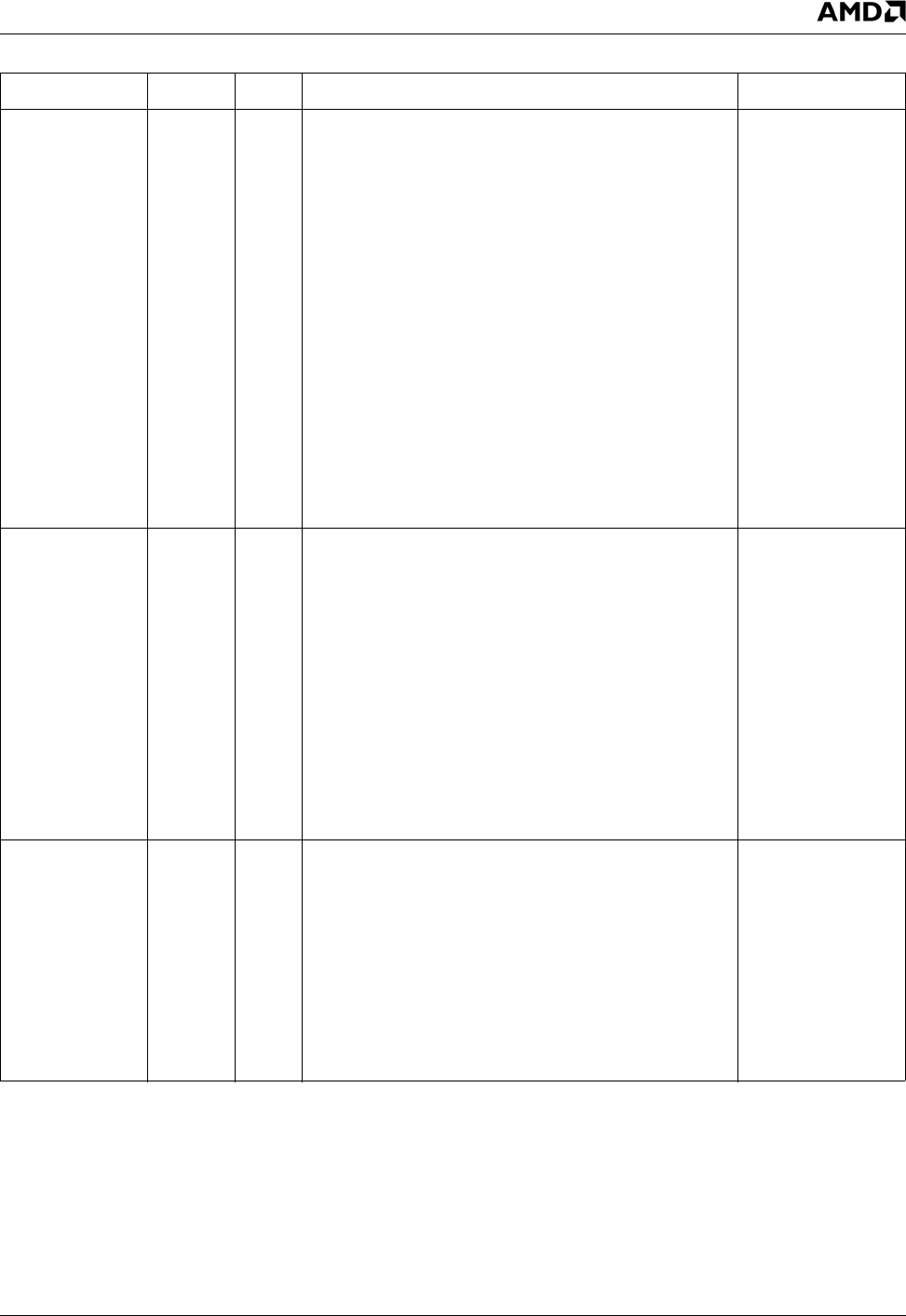

STOP# G1 I/O Target Stop. STOP# is asserted to indicate that the cur-

rent target is requesting that the master stop the current

transaction. This signal is used with DEVSEL# to indicate

retry, disconnect, or target abort. If STOP# is sampled

active by the master, FRAME# is de-asserted and the

cycle is stopped within three PCI clock cycles. As an

input, STOP# can be asserted in the following cases:

1) If a PCI master tries to access memory that has

been locked by another master. This condition is

detected if FRAME# and LOCK# are asserted dur-

ing an address phase.

2) If the PCI write buffers are full or if a previously buff-

ered cycle has not completed.

3) On read cycles that cross cache line boundaries.

This is conditional based upon the programming of

GX1 module’s PCI Configuration Register, Index

41h[1].

This signal is internally connected to a pull-up resistor.

D15

LOCK# H3 I/O Lock Operation. LOCK# indicates an atomic operation

that may require multiple transactions to complete. When

LOCK# is asserted, non-exclusive transactions may pro-

ceed to an address that is not currently locked (at least

16 bytes must be locked). A grant to start a transaction

on PCI does not guarantee control of LOCK#. Control of

LOCK# is obtained under its own protocol in conjunction

with GNT#.

It is possible for different agents to use PCI while a single

master retains ownership of LOCK#. The arbiter can

implement a complete system lock. In this mode, if

LOCK# is active, no other master can gain access to the

system until the LOCK# is de-asserted.

This signal is internally connected to a pull-up resistor.

---

DEVSEL# E4 I/O Device Select. DEVSEL# indicates that the driving

device has decoded its address as the target of the cur-

rent access. As an input, DEVSEL# indicates whether

any device on the bus has been selected. DEVSEL# is

also driven by any agent that has the ability to accept

cycles on a subtractive decode basis. As a master, if no

DEVSEL# is detected within and up to the subtractive

decode clock, a master abort cycle is initiated (except for

special cycles which do not expect a DEVSEL#

returned).

This signal is internally connected to a pull-up resistor.

BHE#

3.4.7 PCI Bus Interface Signals (Continued)

Signal Name BalL No. Type Description Mux