AMD Geode™ SC1200/SC1201 Processor Data Book 229

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

32579B

8 IRQ8# Source. Selects the interface source of the IRQ8# signal.

0: ISA - IRQ8# internal signal. (Connected to internal RTC.)

1: LPC - SERIRQ (ball J31).

7 IRQ7 Source. Selects the interface source of the IRQ7 signal.

0: ISA - IRQ7 (unavailable externally).

1: LPC - SERIRQ (ball J31).

6 IRQ6 Source. Selects the interface source of the IRQ6 signal.

0: ISA - IRQ6 (unavailable externally).

1: LPC - SERIRQ (ball J31).

5 IRQ5 Source. Selects the interface source of the IRQ5 signal.

0: ISA - IRQ5 (unavailable externally).

1: LPC - SERIRQ (ball J31).

4 IRQ4 Source. Selects the interface source of the IRQ4 signal.

0: ISA - IRQ4 (unavailable externally).

1: LPC - SERIRQ (ball J31).

3 IRQ3 Source. Selects the interface source of the IRQ3 signal.

0: ISA - IRQ3 (unavailable externally).

1: LPC - SERIRQ (ball J31).

2 Reserved. Must be set to 0.

1 IRQ1 Source. Selects the interface source of the IRQ1 signal.

0: ISA - IRQ1 (unavailable externally).

1: LPC - SERIRQ (ball J31).

0 IRQ0 Source. Selects the interface source of the IRQ0 signal.

0: ISA - IRQ0 Internal signal. (Connected to OUT0, System Timer, of the internal 8254 PIT.)

1: LPC - SERIRQ (ball J31).

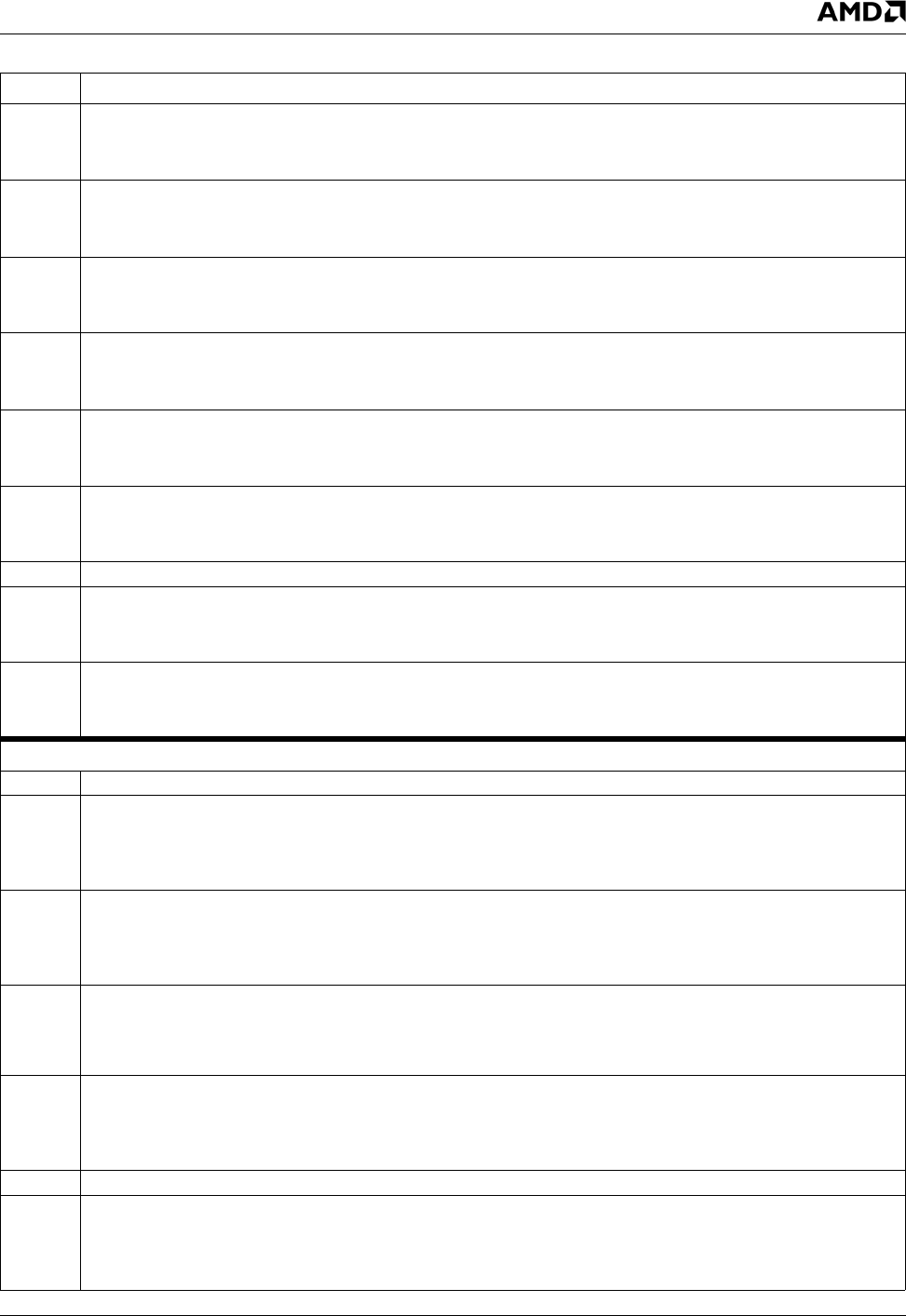

Offset 04h-07h SERIRQ_LVL — Serial IRQ Level Control Register (R/W) Reset Value: 00000000h

31:21 Reserved.

20 INTD# Polarity. If LPC is selected as the interface source for INTD# (F0BAR1+I/O Offset 00h[20] = 1), this bit allows signal

polarity selection.

0: Active high.

1: Active low.

19 INTC# Polarity. If LPC is selected as the interface source for INTC# (F0BAR1+I/O Offset 00h[19] = 1), this bit allows signal

polarity selection.

0: Active high.

1: Active low.

18 INTB# Polarity. If LPC is selected as the interface source for INTB# (F0BAR1+I/O Offset 00h[18] = 1), this bit allows signal

polarity selection.

0: Active high.

1: Active low.

17 INTA# Polarity. If LPC is selected as the interface source for INTA# (F0BAR1+I/O Offset 00h[17] = 1), this bit allows signal

polarity selection.

0: Active high.

1: Active low.

16 Reserved. Must be set to 0.

15 IRQ15 Polarity. If LPC is selected as the interface source for IRQ15 (F0BAR1+I/O Offset 00h[15] = 1), this bit allows signal

polarity selection.

0: Active high.

1: Active low.

Table 6-31. F0BAR1+I/O Offset: LPC Interface Configuration Registers (Continued)

Bit Description