AMD Geode™ SC1200/SC1201 Processor Data Book 317

Video Processor Module

32579B

Bob

The Bob method displays the odd frame followed by the

even frame. If a full-scale image is displayed, each line in

the odd and even field must be vertically doubled (see Sec-

tion 7.2.2.5 "2-Tap Vertical and Horizontal Upscalers" on

page 322) because each odd and each even field only con-

tain one-half a frames worth of data. This means that the

Bob method reduces the video image resolution, but has a

higher effective refresh rate. If there is a change of refresh

rate from the VIP block to the display device, then a field

will sometimes be displayed twice. The advantage of this

method is that the process is simple as only half the data is

transmitted from the GX1 module’s Video Frame Buffer to

the Video Processor per a given amount of time, therefore

reducing the memory bandwidth requirement. The disad-

vantage is that there are some observable visual effects

due to the reduction in resolution.

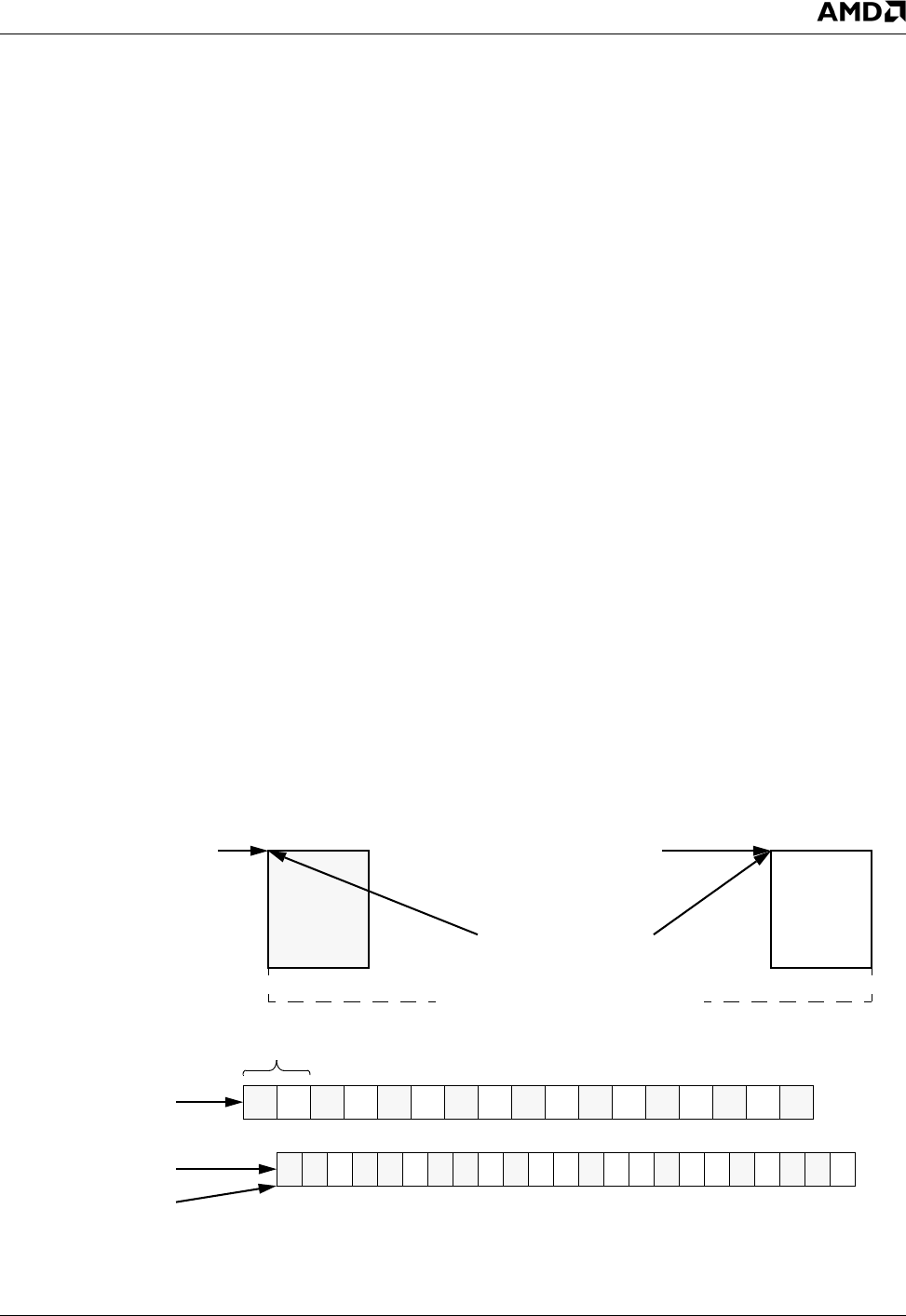

Figure 7-5 is an example of how the Bob method is per-

formed. The example assumes that the display device is a

CRT at 85 Hz refresh and single buffering is used for the

data. The example does not assume anything regarding

scaling that may be performed in the Video Processor. The

example is only presented to allow for a general under-

standing of how the SC1200/SC1201 processor’s video

support hardware works and not as an all-inclusive state-

ment of operation.

The following procedure is an example of how to create a

Bob method. This example assumes single buffering in the

GX1 module’s video frame buffer. The Video Processor

registers that control the VIP bus master only need to be

initialized.

1) Program the VIP bus master address registers.

Three registers control where the VIP video data is

stored in the GX1 module’s frame buffer:

– F4BAR2+Memory Offset 20h – Video Data Odd

Base Address

– F4BAR2+Memory Offset 24h – Video Data Even

Base Address

– F4BAR2+Memory Offset 28h – Video Data Pitch

The Video Data Even Base Address must be sepa-

rated from the Video Data Odd Base Address by at

least the field data size. The Video Data Pitch register

must be programmed to 00000000h.

2) Program other VIP bus master support registers.

In F4BAR2+Memory Offset 00h, make sure that the

VIP FIFO bus request threshold is set to 32 bytes (bit

22 = 1) and that the Video Input Port mode is set to

CCIR-656. An interrupt needs to be generated so that

the GX1 module’s video frame buffer pointer can flip to

the field that has completed transfer to the video frame

buffer. So in F4BAR2+Memory Offset 04h, enable the

Field Interrupt bit. Auto-Flip is normally set to allow the

CCIR-656 Decoder to identify which field is being pro-

cessed. Capture video data needs to be enabled and

Run Mode Capture is set to Start Capture at beginning

of next field. Data is now being captured to the frame

buffer.

3) Field Interrupt.

When the field interrupt occurs, the interrupt handler

must program the GX1 module’s video buffer start off-

set value (GX_BASE+Memory Offset 8320h) with the

address of the field that was just received from the VIP

interface. This action will cause the display controller

to ping-pong between the two fields. The new address

will not take affect until the start of a new display con-

troller frame. The field that was just received can be

known by reading the Current Field bit at

F4BAR2+Memory Offset 08h[24].

Figure 7-5. Capture Video Mode Bob Example Using One Video Frame Buffer

Video Data Odd Base Video Data Even Base

DC_VID_ST_OFFSET

Odd

Field

Even

Field

GX1 Module’s Video Frame Buffer

1234567891011121314151617

1234 67891011121314151617181920 2223

Capture video fill

Video subsystem

85 frames per second

5

5

21

30 frames per second

(F4BAR2+Memory Offset 24h)

Address not changed during runtime

(GX_BASE+Memory Offset 8320h)

Ping-pongs between the two buffers during runtime

(F4BAR2+Memory Offset 20h)

Address not changed

during runtime

Buf #1

sequence

empty sequence