80

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.9 SUBC (Subtract Word Data in Source Register and Carry

Bit from Destination Register)

Subtracts the word data in "Rj" and the carry bit from the word data in "Ri", stores

results to "Ri".

■ SUBC (Subtract Word Data in Source Register and Carry Bit from Destination

Register)

Assembler format: SUBC Rj, Ri

Operation: Ri – Rj – C → Ri

Flag change:

N : Set when the MSB of the operation result is "1", cleared when the MSB is "0".

Z : Set when the operation result is "0", cleared otherwise.

V : Set when an overflow has occurred as a result of the operation, cleared otherwise.

C : Set when a borrow has occurred as a result of the operation, cleared otherwise.

Execution cycles: 1 cycle

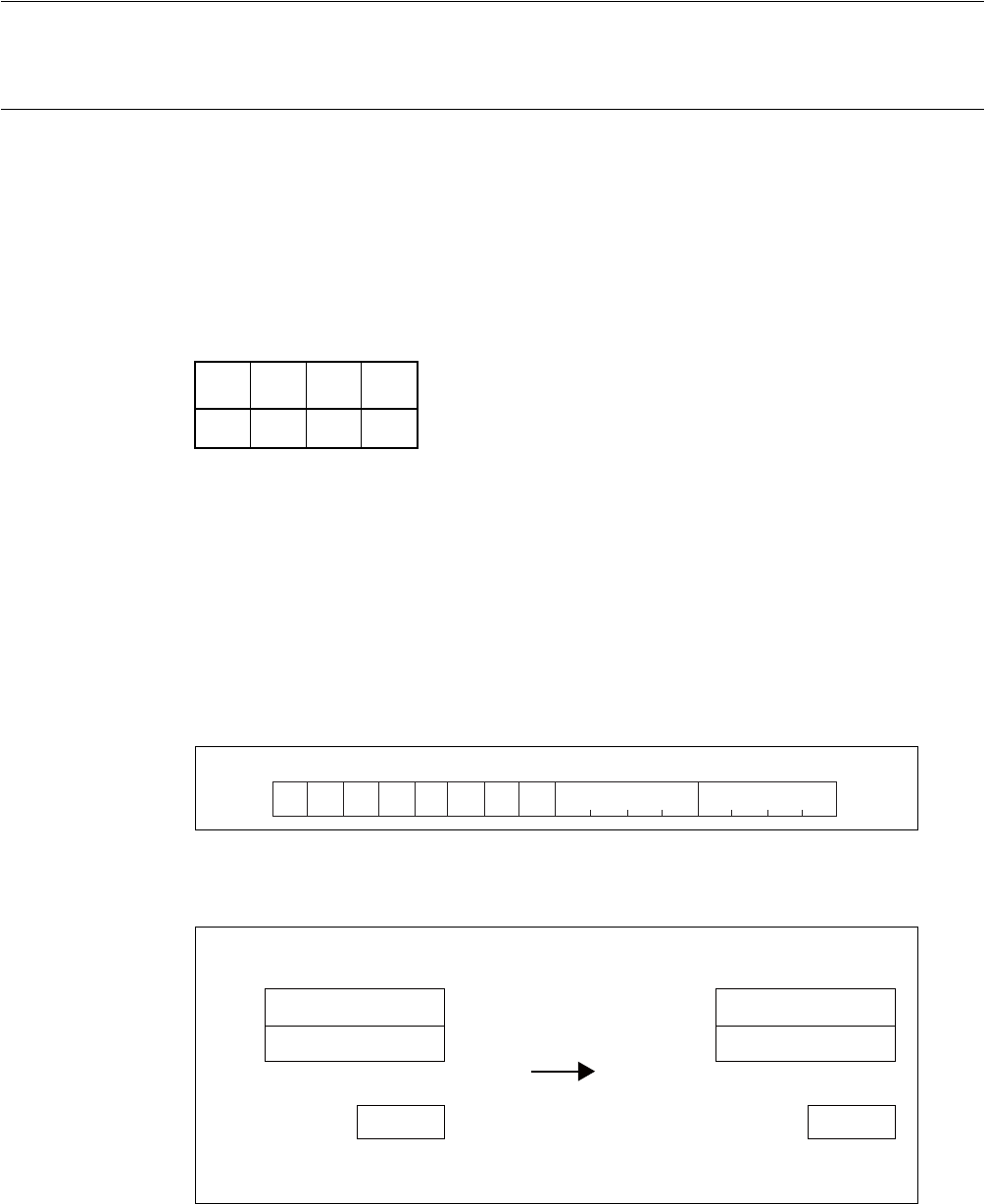

Instruction format:

Example: SUBC R2, R3

NZVC

CCCC

MSB LSB

10101101 Rj Ri

R2

R3

1234 5678

9999 9999

NZVC

CCR

R2

R3

CCR

0001

NZVC

1000

8765 4320

1234 5678

Before execution After execution

Instruction bit pattern : 1010 1101 0010 0011