172

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.76 STH (Store Half-word Data in Register to Memory)

Stores the half-word data in "Ri" to memory address "Rj".

■ STH (Store Half-word Data in Register to Memory)

Assembler format: STH Ri, @Rj

Operation: Ri → (Rj)

Flag change:

N, Z, V, and C: Unchanged

Execution cycles: a cycle(s)

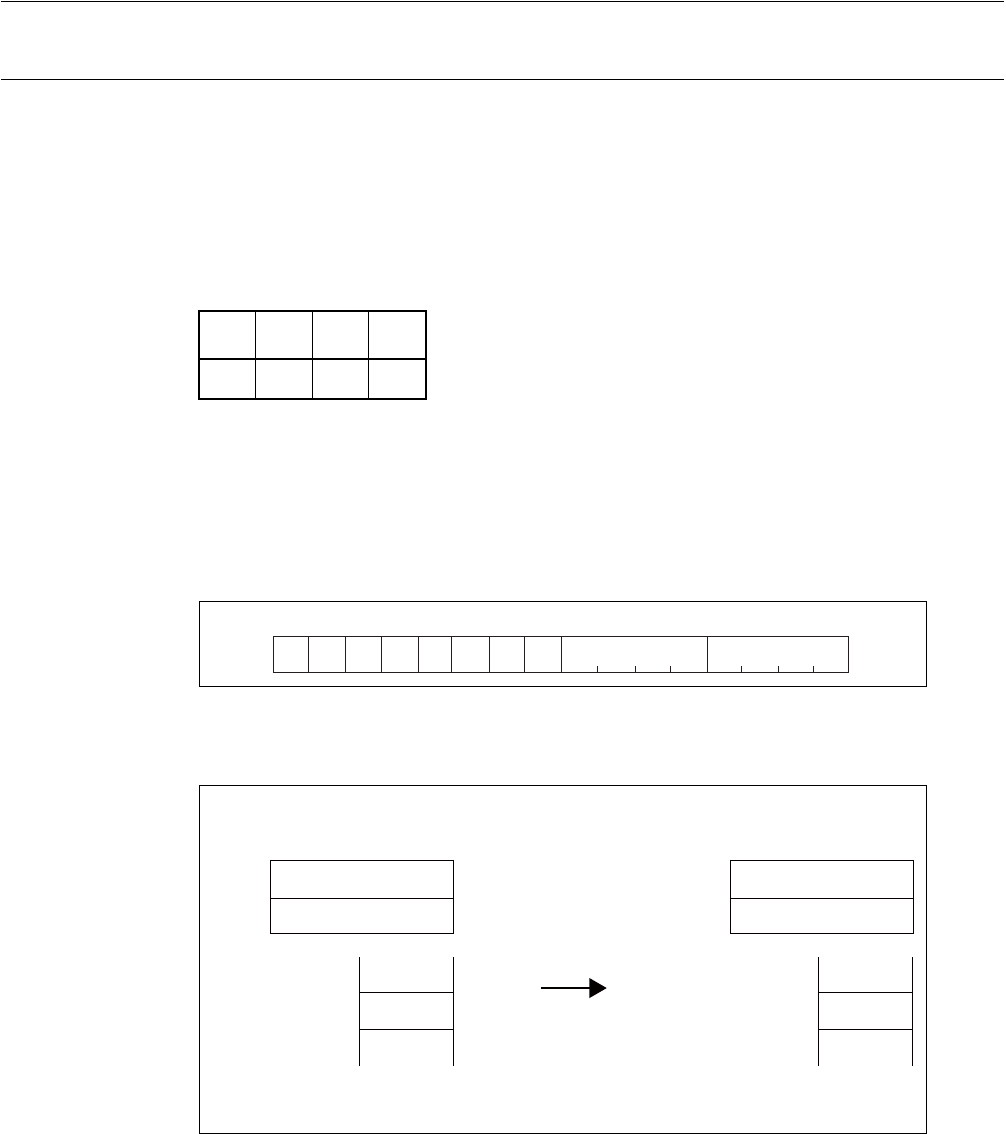

Instruction format:

Example: STH R3, @R2

NZVC

––––

MSB LSB

00010101 Rj Ri

R2

12345678

1234 5678

0000 4321

R2

R3R3

0000 4321

1234 5678

12345678

4321

xxxx

Memory Memory

Before execution After execution

Instruction bit pattern : 0001 0101 0010 0011