7

CHAPTER 2 MEMORY ARCHITECTURE

2.1.1 Direct Address Area

The lower portion of the address space is used for the direct address area. Instructions

that specify direct addresses allow you to access this area without the use of general-

purpose registers, using only the operand information in the instruction itself. The size

of the address area that can be specified by direct addressing varies according to the

length of the data being transferred.

■ Direct Address Area

The size of the address area that can be specified by direct addressing varies according to the length of the

data being transferred, as follows:

• Transfer of byte data: 0000 0000

H

to 0000 00FF

H

• Transfer of half-word data: 0000 0000

H

to 0000 01FF

H

• Transfer of word data: 0000 0000

H

to 0000 03FF

H

■ Use of Operand Information Contained in Instructions

The 8-bit address information contained in the instruction has the following significance.

• In byte data: Value represents the lower 8 bits of the address.

• In half-word data: Value is doubled and used as the lower 9 bits of the address.

• In word data: Value is multiplied by 4 and used as the lower 10 bits of the address.

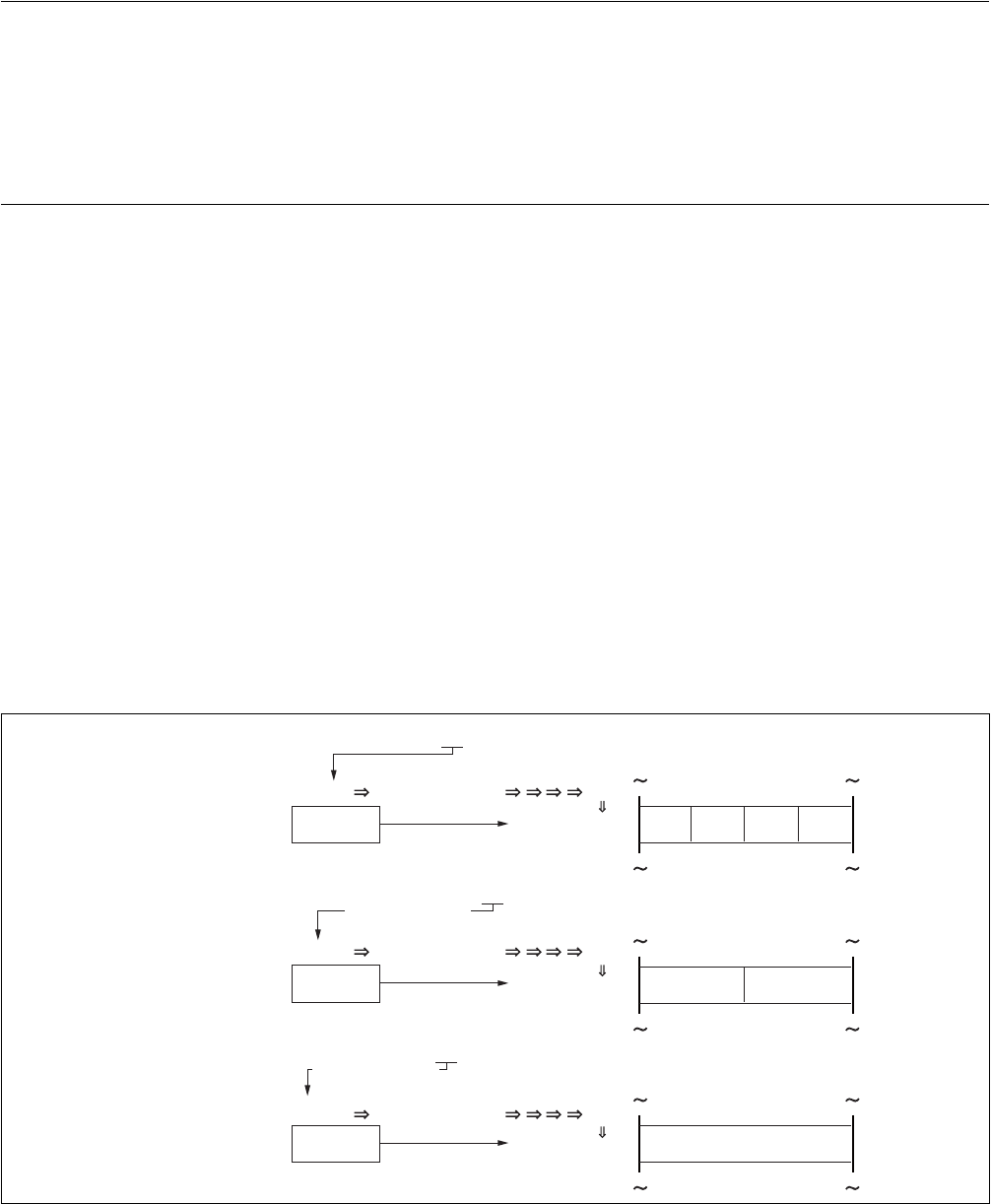

Figure 2.1-2 shows the relationship between the length of the data that designates the direct address, and

the actual address in memory.

Figure 2.1-2 Relation between Direct Address Data and Memory Address Value

[Example 1] Byte data: DMOVB R13,@58H

[Example 2] Half-word data: DMOVH R13,@58H

[Example 3] Word data: DMOV R13,@58H

Object code:1A58H

0000 0058HR13 12345678

0000 0058

HR13 12345678

0000 0058

HR13 12345678

Right 1-bit shift

Right 2-bit shift

Memory space

Memory space

Memory space

78

5678

1345678

58

H

No data shift

Object code:192C

H 58HLeft 1-bit shift

Object code:1816

H 58HLeft 2-bit shift