174

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.78 STH (Store Half-word Data in Register to Memory)

Stores the half-word data in "Ri" to memory address "(R14 + o8 × 2)".

The value "o8" is a signed calculation.

■ STH (Store Half-word Data in Register to Memory)

Assembler format: STH Ri, @(R14, disp9)

Operation: Ri → ( R14 + o8 × 2)

Flag change:

N, Z, V, and C: Unchanged

Execution cycles: a cycle(s)

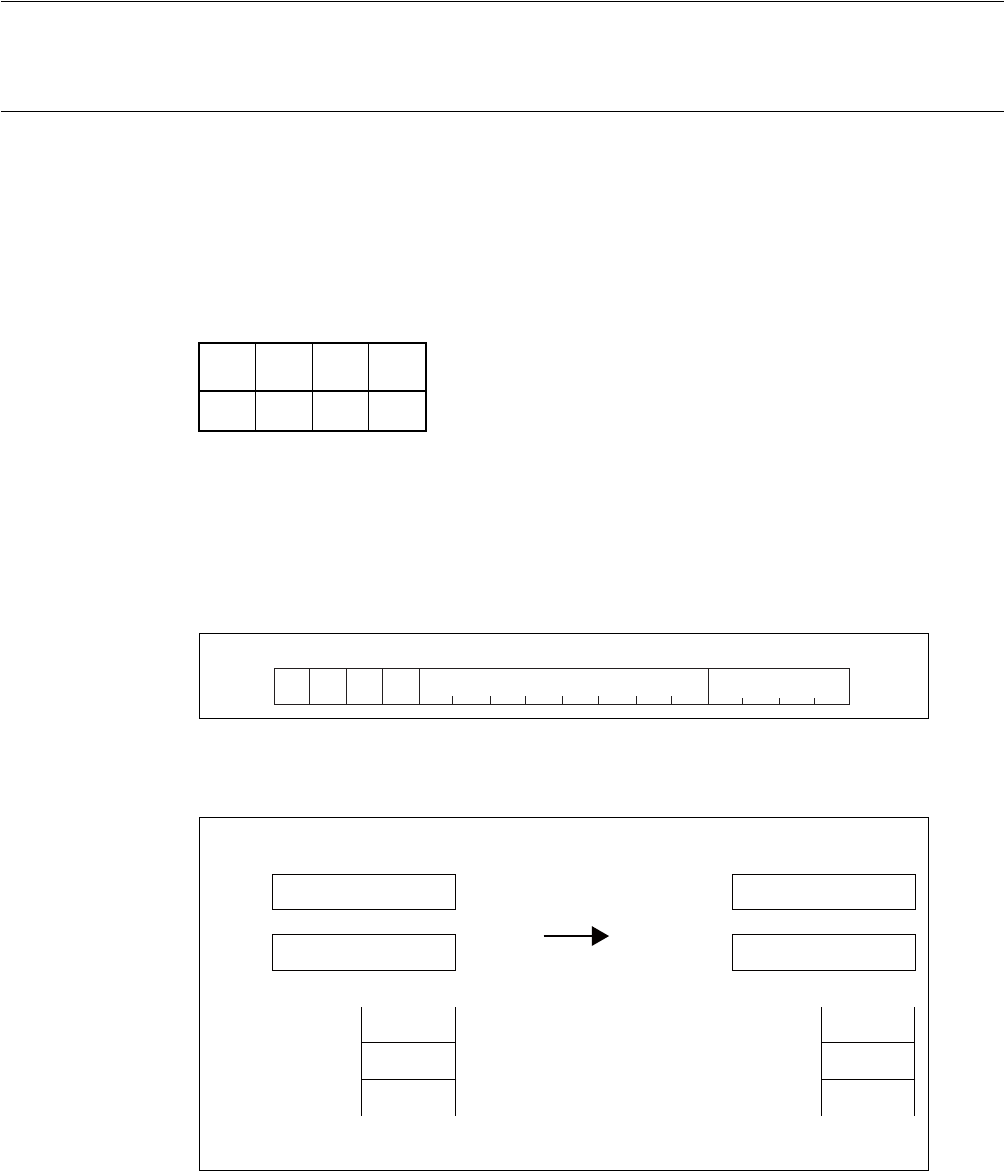

Instruction format:

Example: STH R3, @(R14, 2)

NZVC

––––

MSB LSB

0101 Rio8

12345678

R3R3

0000 4321

4321

12345678

1234567A 1234567A

1234 5678

0000 4321

R14

1234 5678

R14

Instruction bit pattern : 0101 0000 0001 0011

xxxx

Memory Memory

Before execution After execution