196

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.95 JMP:D (Jump)

This branching instruction has a delay slot.

Branches to the address indicated by "Ri".

■ JMP:D (Jump)

Assembler format: JMP : D @Ri

Operation: Ri → PC

Flag change:

N, Z, V, and C: Unchanged

Execution cycles: 1 cycle

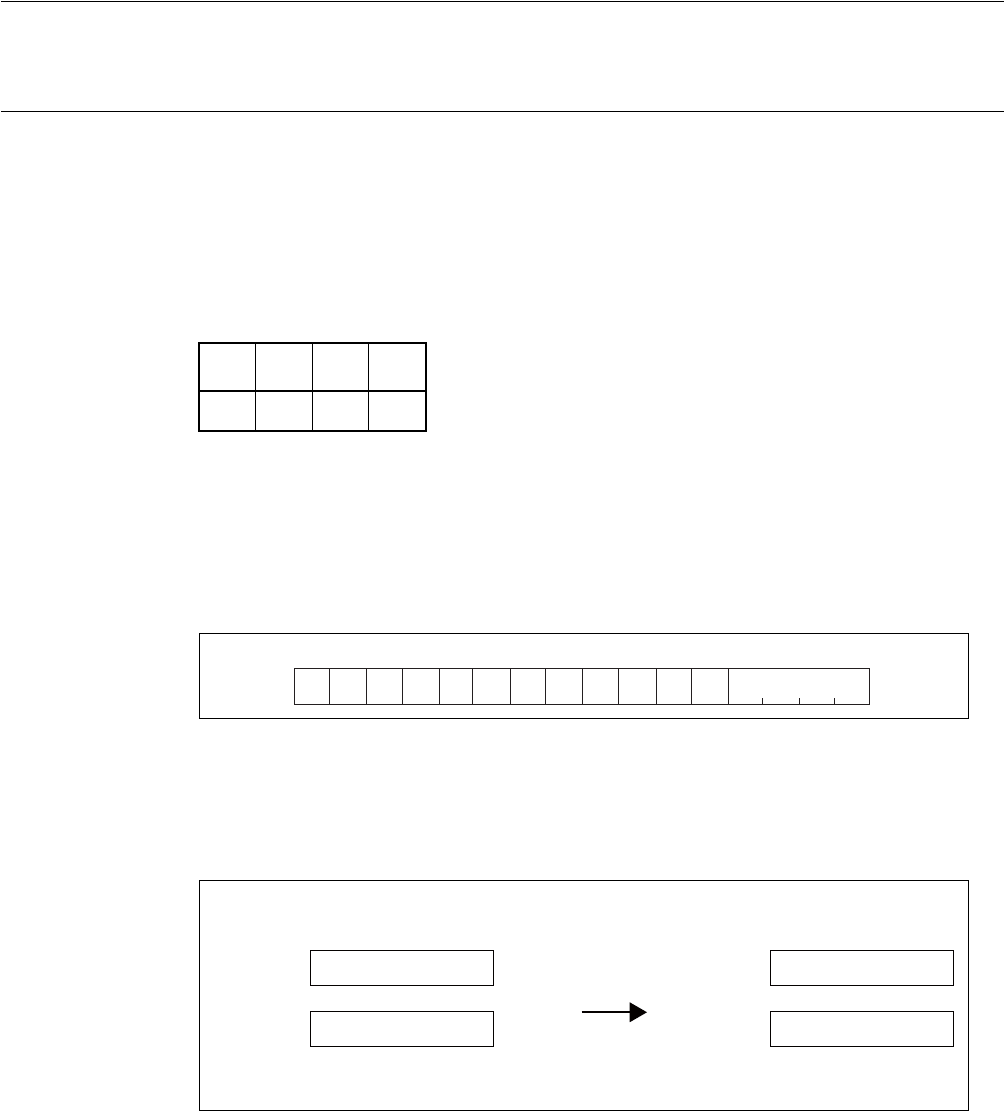

Instruction format:

Example: JMP : D @R1

LDI : 8 #0FFH, R1 ; Instruction placed in delay slot

The instruction placed in the delay slot will be executed before execution of the branch destination

instruction.

The value "R1" above will vary according to the specifications of the "LDI:8" instruction placed in

the delay slot.

NZVC

––––

MSB LSB

100111110000 Ri

...

R1R1

0000 00FF

FF80 0000

C000 8000

PC

C000 8000

PC

Before execution of "JMP" instruction After branching

Instruction bit pattern : 1001 1111 0000 0001