235

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.119 COPSV (Save 32-bit Data from Coprocessor Register to

Register)

Transfers the 16-bit data consisting of parameters "CC", "CRj", "Ri" to the coprocessor

indicated by channel number u4, then on the next cycle loads the data output by the

coprocessor to CPU general-purpose register "Ri".

Basically, this operation transfers data from a register within the coprocessor. The

32-bit data stored in coprocessor register "CRj" is transferred to CPU general-purpose

register "Ri". Note that the actual interpretation of the fields "CC", "CRj", "Ri" is done

by the coprocessor so that the detailed actual operation is determined by the

specifications of the coprocessor.

If the coprocessor designated by the value "u4" is not mounted, a "coprocessor not

found" trap is generated.

However, no "coprocessor error" trap will be generated even if the coprocessor

designated by the value "u4" has generated an error in a previous operation.

The operation of this instruction is basically identical to "COPST", except for the above

difference in the operation of the error trap.

■ COPSV (Save 32-bit Data from Coprocessor Register to Register)

Assembler format: COPSV #u4, #CC, CRj, Ri

Operation: CC, CRj, Ri → Coprocessor on channel u4

CRj → Ri

Flag change:

N, Z, V, and C: Unchanged

Execution cycles: 1 + 2a cycles

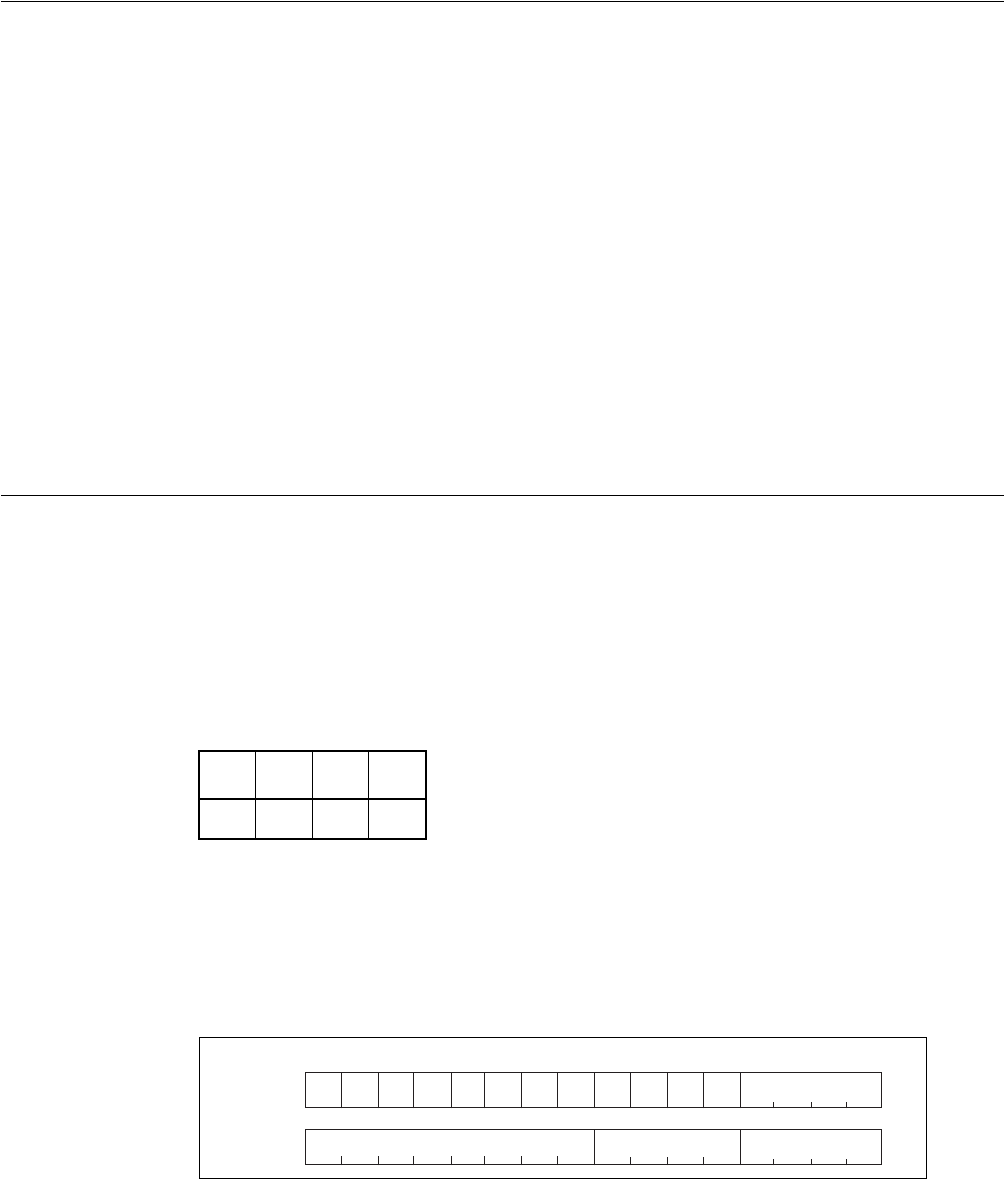

Instruction format:

NZVC

––––

MSB LSB

100111111111 u4(n+0)

RiCRjCC(n+2)