124

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.36 MULH (Multiply Half-word Data)

Multiplies the half-word data in the lower 16 bits of "Rj" by the half-word data in the

lower 16 bits of "Ri" as signed numbers, and stores the resulting signed 32-bit data in

the multiplication/division register (MDL).

The multiplication/division register (MDH) is undefined.

■ MULH (Multiply Half-word Data)

Assembler format: MULH Rj, Ri

Operation: Rj × Ri → MDL

Flag change:

N: Set when the MSB of the "MDL" of the operation result is "1", cleared when the MSB is "0".

Z: Set when the "MDL" of the operation result is "0", cleared otherwise.

V: Unchanged

C: Unchanged

Execution cycles: 3 cycles

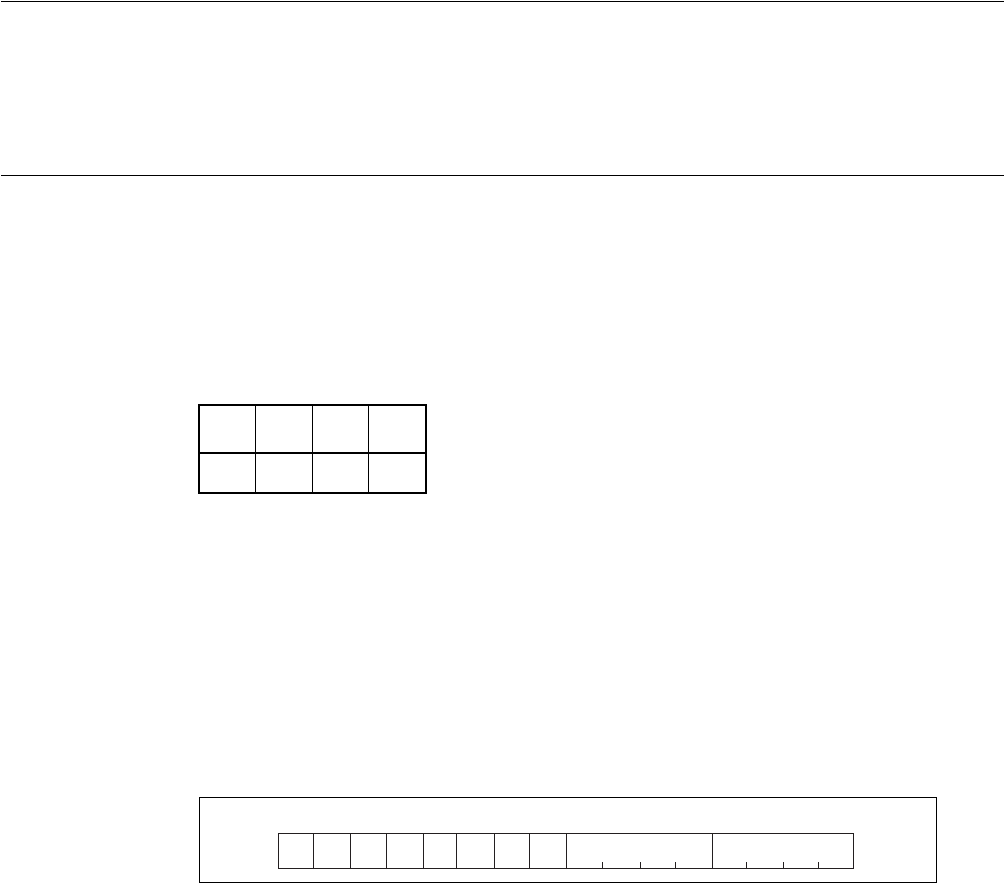

Instruction format:

NZVC

CC– –

MSB LSB

10111111 Rj Ri