275

APPENDIX B Instruction Maps

B.1 Instruction Map

This section shows instruction maps for FR family CPU.

■ Instruction Map

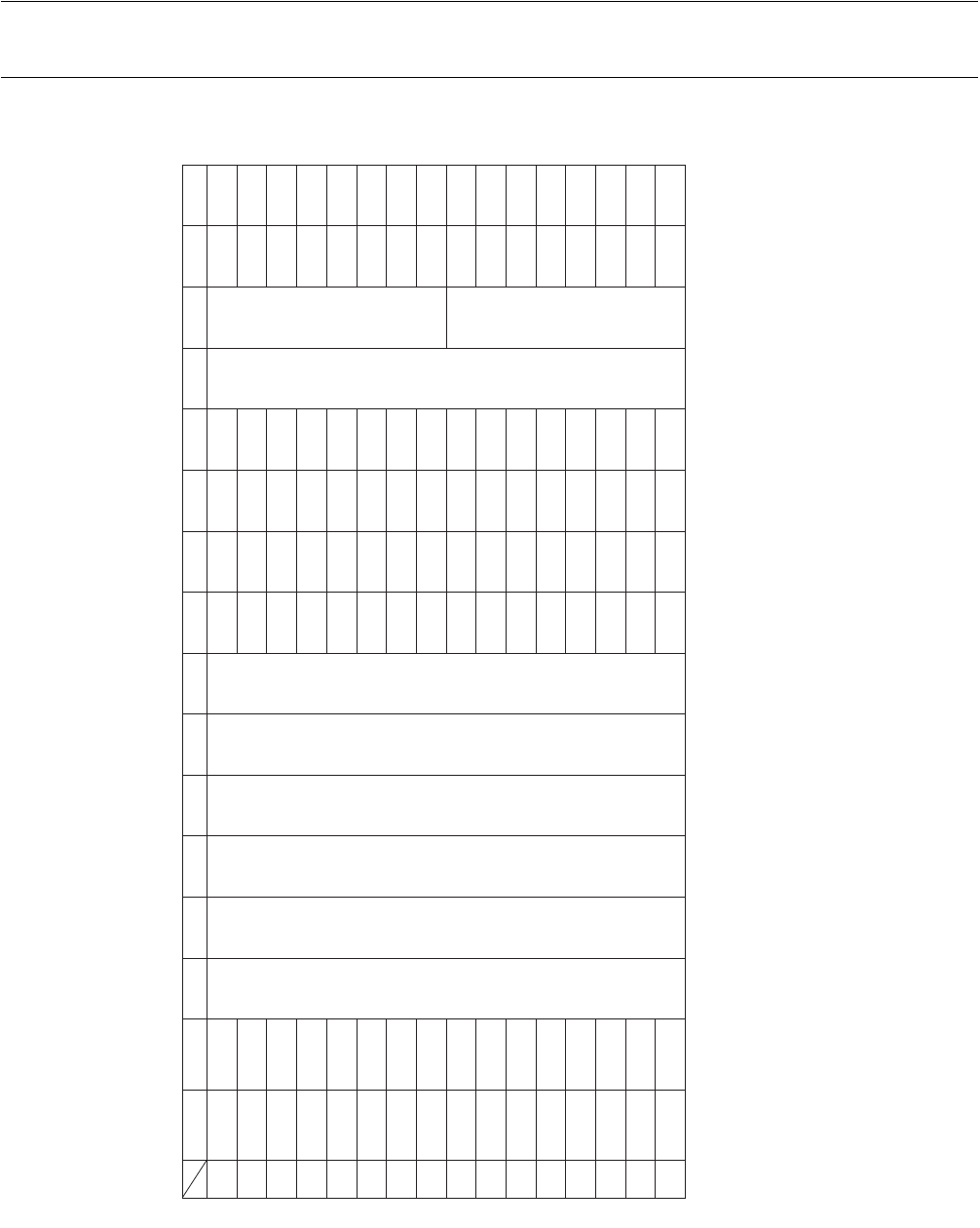

Table B.1-1 Instruction Map

Higher 4 bits

0 1 23456789ABCDEF

0 LD @(R13,Rj),

Ri

ST Ri,

@(R13,Rj)

LD @(R14,

disp10),Ri

ST Ri,@

(R14,

disp10)

LDUH

@(R14,

disp9),Ri

STH

Ri,@(R14,

disp9)

LDUB

@(R14,

disp8),Ri

STB

Ri,@(R14,

disp8)

BANDL

#u4,@Ri

BORL

#u4,@Ri

ADDN #i4,Ri LSR #u4,Ri

LDI:8 #i8,Ri

CALL

label12

BRA label9 BRA:D

label9

1 LDUH

@(R13,Rj), Ri

STH Ri,

@(R13,Rj)

BANDH

#u4,@Ri

BORH

#u4,@Ri

ADDN2

#i4,Ri

LSR2 #u4,Ri BNO label9 BNO:D

label9

2 LDUB

@(R13,Rj), Ri

STB Ri,

@(R13,Rj)

AND Rj,Ri OR Rj,Ri ADDN Rj,Ri LSR Rj,Ri BEQ label9 BEQ:D

label9

3 LD @(R15,

udisp6),Ri

ST Ri,

@(R15,ud6)

ANDCCR

#u8

ORCCR

#u8

ADDSP

#s10

MOV Ri,Rs BNE label9 BNE:D

label9

4 LD @Rj,Ri ST Ri,@Rj AND Rj,@Ri OR Rj,@Ri ADD #i4,Ri LSL #u4,Ri BC label9 BC:D

label9

5 LDUH @Rj,Ri STH Ri,@Rj ANDH

Rj,@Ri

ORH

Rj,@Ri

ADD2 #i4,Ri LSL2 #u4,Ri BNC label9 BNC:D

label9

6 LDUB @Rj,Ri STB Ri,@Rj ANDB

Rj,@Ri

ORB Rj,@Ri ADD Rj,Ri LSL Rj,Ri BN label9 BN:D

label9

7 E format E format STILM #u8 E format ADDC Rj,Ri MOV Rs,Ri BP label9 BP:D

label9

8DMOV

@d10,R13

DMOV

R13,@d10

BTSTL

#u4,@Ri

BEORL

#u4,@Ri

CMP #i4,Ri ASR #u4,Ri

CALL:D

label12

BV label9 BV:D

label9

9DMOVH ,

R13

DMOVH

R13, @d9

BTSTH

#u4,@Ri

BEORH

#u4,@Ri

CMP2 #i4,Ri ASR2

#u4,Ri

BNV label9 BNV:D

label9

A DMOVB @d8,

R13

DMOVB

R13, @d8

XCHB

@Rj,Ri

EOR Rj,Ri CMP Rj,Ri ASR Rj,Ri BLT label9 BLT:D label9

BDMOV

@d10,@–R15

DMOV

@R15+,@d10

MOV Rj,Ri LD:20

#i20,Ri

MULU Rj,Ri MULUH

Rj,Ri

BGE label9 BGE:D

label9

CDMOV

@d10,@R13+

DMOV

@R13+,@d10

LDM0

(reglist)

EOR Rj,@Ri SUB Rj,Ri LDRES

@Ri+,#u4

BLE label9 BLE:D

label9

DDMOVH ,

@R13+

DMOVH

@R13+, @d9

LDM1

(reglist)

EORH

Rj,@Ri

SUBC Rj,Ri STRES

#u4,@Ri+

BGT label9 BGT:D

label9

E DMOVB

@d8, @R13+

DMOVB

@R13+, @d8

STM0

(reglist)

EORB

Rj,@Ri

SUBN Rj,Ri BLS label9 BLS:D

label9

F ENTER #u10 INT #u8 STM1

(reglist)

E format MUL Rj,Ri MULH Rj,Ri BHI label9 BHI:D

label9

Lower 4 bits

@d9

@d9