258

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.135 XCHB (Exchange Byte Data)

Exchanges the contents of the byte address indicated by "Rj" and those indicated by

"Ri".

The lower 8 bits of data originally at "Ri" are transferred to the byte address indicated

by "Rj", and the data originally at "Rj" is extended with zeros and transferred to "Ri".

The CPU will not accept hold requests between the memory read operation and the

memory write operation of this instruction.

■ XCHB (Exchange Byte Data)

Assembler format: XCHB @Rj, Ri

Operation: Ri → TEMP

extu ((Rj)) → Ri

TEMP → (Rj)

Flag change:

N, Z, V, and C: Unchanged

Execution cycles: 2a cycles

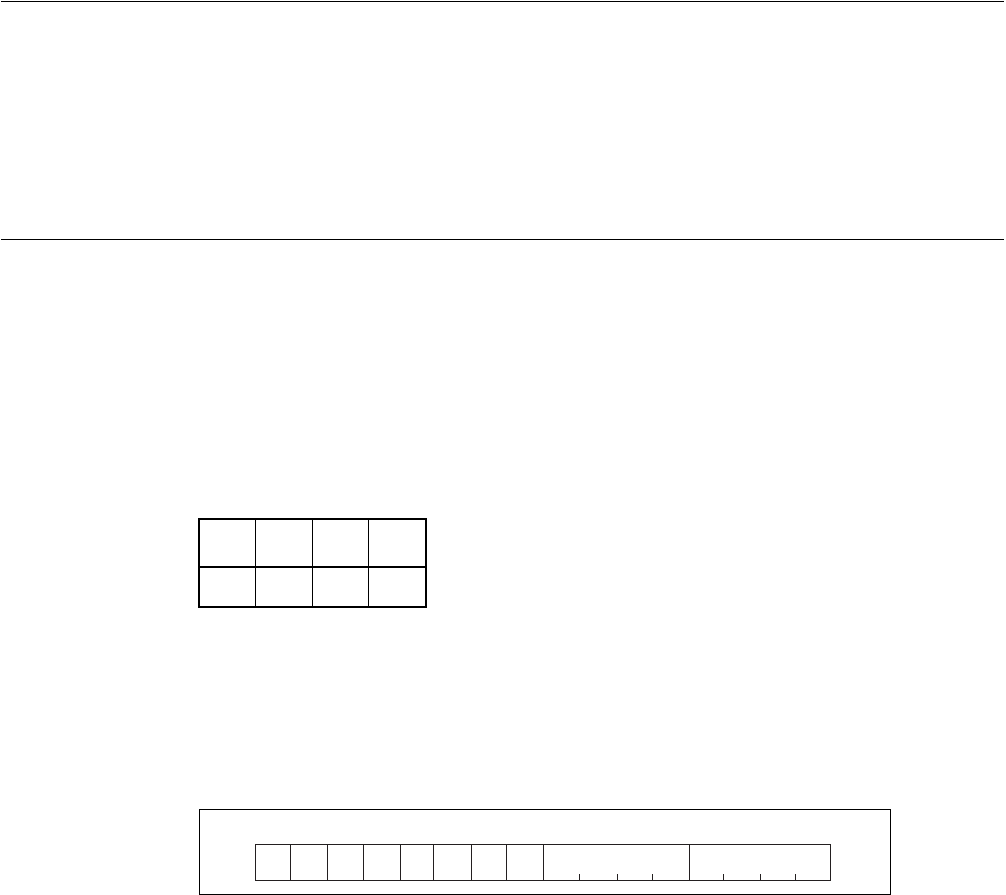

Instruction format:

NZVC

––––

MSB LSB

10001010 Rj Ri