83

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.12 CMP (Compare Immediate Data of Source Register and

Destination Register)

Subtracts the result of the higher 28 bits of 4-bit immediate data with zero extension

from the word data in "Ri", places results in the condition code register (CCR).

■ CMP (Compare Immediate Data of Source Register and Destination Register)

Assembler format: CMP #i4, Ri

Operation: Ri – extu(i4)

Flag change:

N : Set when the MSB of the operation result is "1", cleared when the MSB is "0".

Z : Set when the operation result is "0", cleared otherwise.

V : Set when an overflow has occurred as a result of the operation, cleared otherwise.

C : Set when a carry has occurred as a result of the operation, cleared otherwise.

Execution cycles: 1 cycle

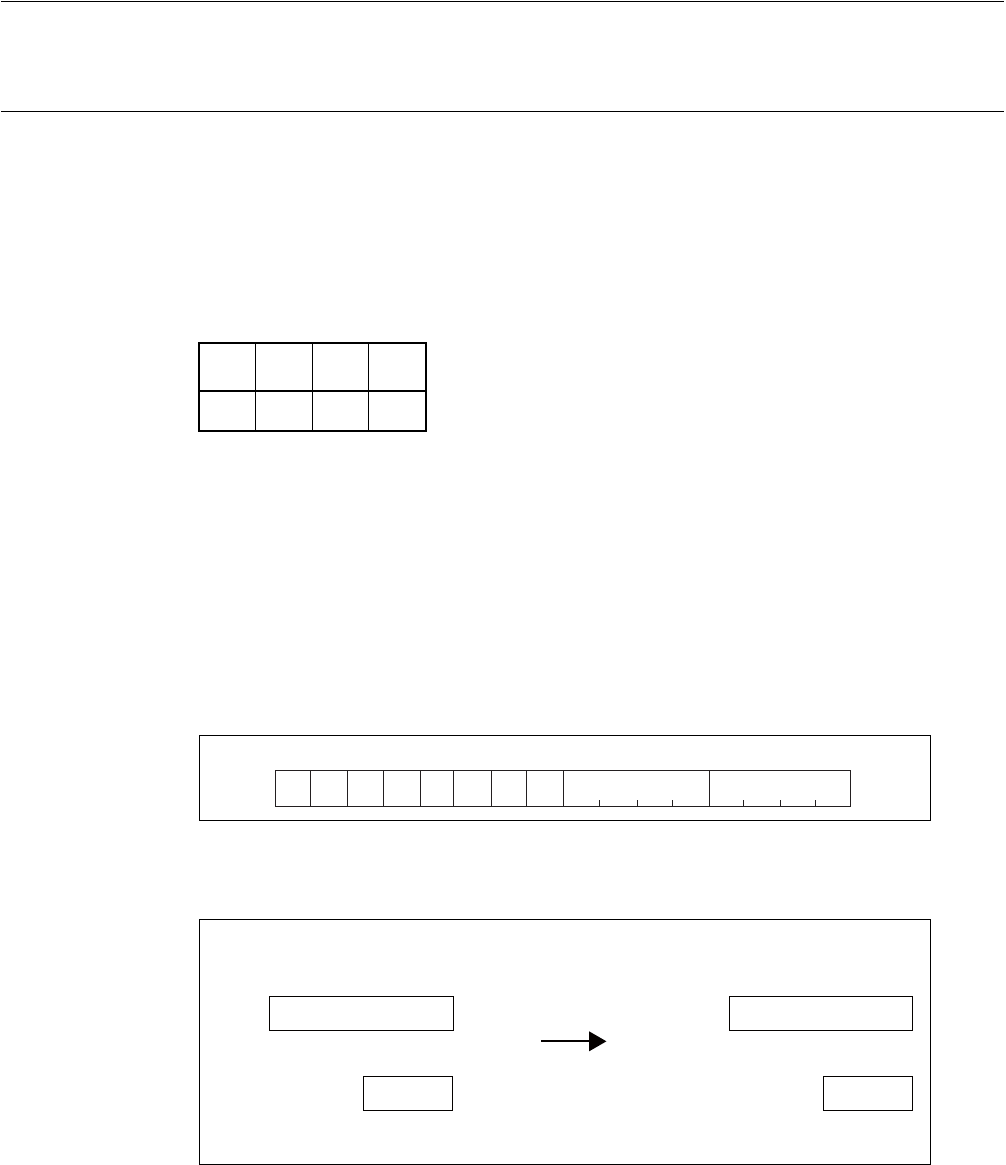

Instruction format:

Example: CMP #3, R3

NZVC

CCCC

MSB LSB

10101000 i4 Ri

R3

0000 0003

NZVC

CCR

R3

CCR

0000

NZVC

0100

0000 0003

Instruction bit pattern : 1010 1000 0011 0011

Before execution After execution