238

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.121 ANDCCR (And Condition Code Register and Immediate

Data)

Takes the logical AND of the byte data in the condition code register (CCR) and the

immediate data, and returns the results into the "CCR".

■ ANDCCR (And Condition Code Register and Immediate Data)

Assembler format: ANDCCR #u8

Operation: CCR and u8 → CCR

Flag change:

S, I, N, Z, V, and C: Varies according to results of calculation.

Execution cycles: c cycle(s)

The number of execution cycles is normally "1". However, if the instruction immediately after

involves read or write access to memory address "R15", the system stack pointer (SSP) or the user

stack pointer (USP), then an interlock is applied and the value becomes 2 cycles.

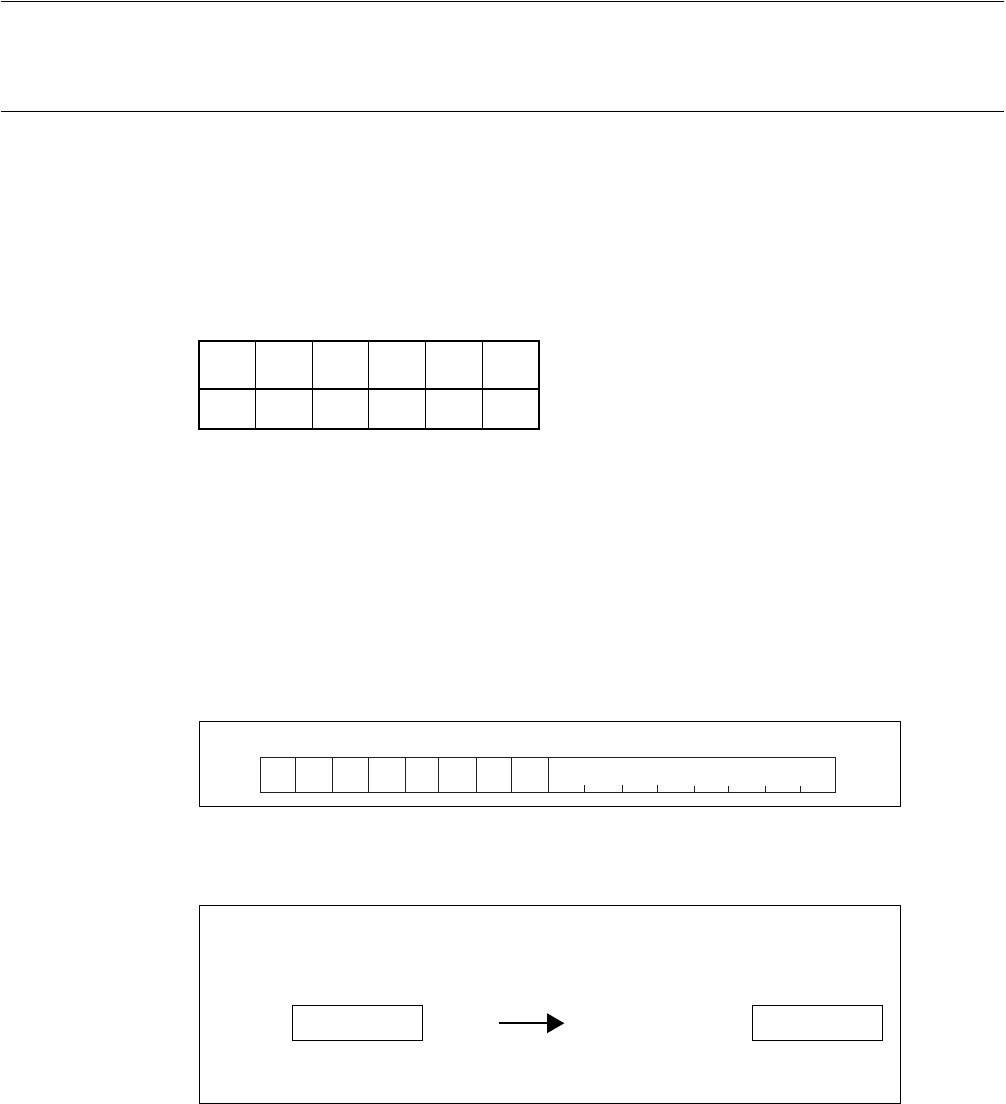

Instruction format:

Example: ANDCCR #0FEH

SINZVC

CCCCCC

MSB LSB

10000011

u8

CCR CCR

010101

SINZVC

010100

SINZVC

Before execution After execution

Instruction bit pattern : 1000 0011 1111 1110