60

CHAPTER 5 PRECAUTIONARY INFORMATION FOR THE FR FAMILY CPU

5.4.1 Processing Non-delayed Branching Instructions

The FR family CPU processes non-delayed branching instructions in the order in which the

program is written, introducing a 1-cycle delay in execution speed if branching takes place.

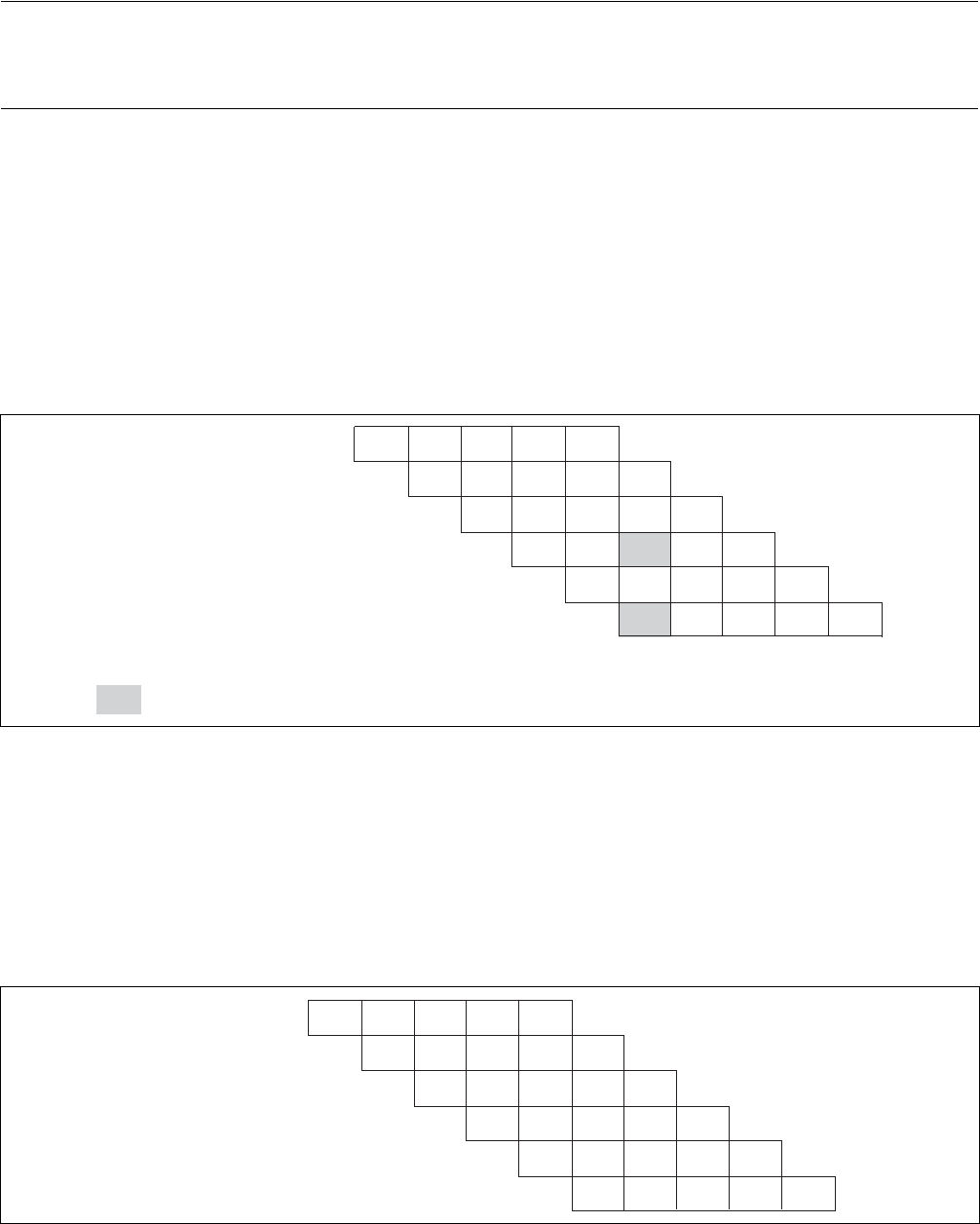

■ Examples of Processing Non-delayed Branching Instructions

Figure 5.4-1 shows an example of processing a non-delayed branching instruction when branching

conditions are satisfied.

In this example, the instruction "ST R2,@R12" (which immediately follows the branching instruction) has

entered the pipeline operation before the fetching of the branch destination instruction, but is canceled

during execution.

As a result, the program is processed in the order in which it is written, and the branching instruction

requires an apparent processing time of two cycles.

Figure 5.4-1 Example: Processing a Non-delayed Branching Instruction (Branching Conditions Satisfied)

Figure 5.4-2 shows an example of processing a non-delayed branching instruction when branching

conditions are not satisfied.

In this example, the instruction "ST R2,@R12" (which immediately follows the branching instruction) has

entered the pipeline operation before the fetching of the branch destination instruction, and is executed

without being canceled.

Because instructions are executed without branching, the program is processed in the order in which it is

written. The branching instruction requires an apparent processing time of one cycle.

Figure 5.4-2 Example: Processing a Non-delayed Branching Instruction (Branching Conditions Not Satisfied)

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF -- -- -- --

-- : Canceled stages

: PC change

IF ID EX MA WB

LD @R10, R1

LD @R11, R2

ADD R1, R3

BNE TestOK(branching conditions satisfied)

ST R2, @R12(instruction immediately after)

ST R2, @R13(branch destination instruction)

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

IF ID EX MA WB

Not canceled

IF ID EX MA WB

LD @R10, R1

LD @R11, R2

ADD R1, R3

BNE TestOK(branching conditions not satisfied)

ST R2, @R12(instruction immediately after)

ADD #4, R12(subsequent instruction)