250

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.131 STM0 (Store Multiple Registers)

The "STM0" instruction accepts registers in the range R0 to R7 as members of the

parameter "reglist" (See Table 7.131-1.) .

Registers are processed in descending numerical order.

■ STM0 (Store Multiple Registers)

Assembler format: STM0 (reglist)

Operation: The following operations are repeated according to the number of registers specified in the

parameter "reglist".

R15 – 4 → R15

Ri → (R15)

Flag change:

N, Z, V, and C: Unchanged

Execution cycles: If "n" is the number of registers specified in the parameter "reglist", the execution cycles

required are as follows.

a × n + 1 cycle

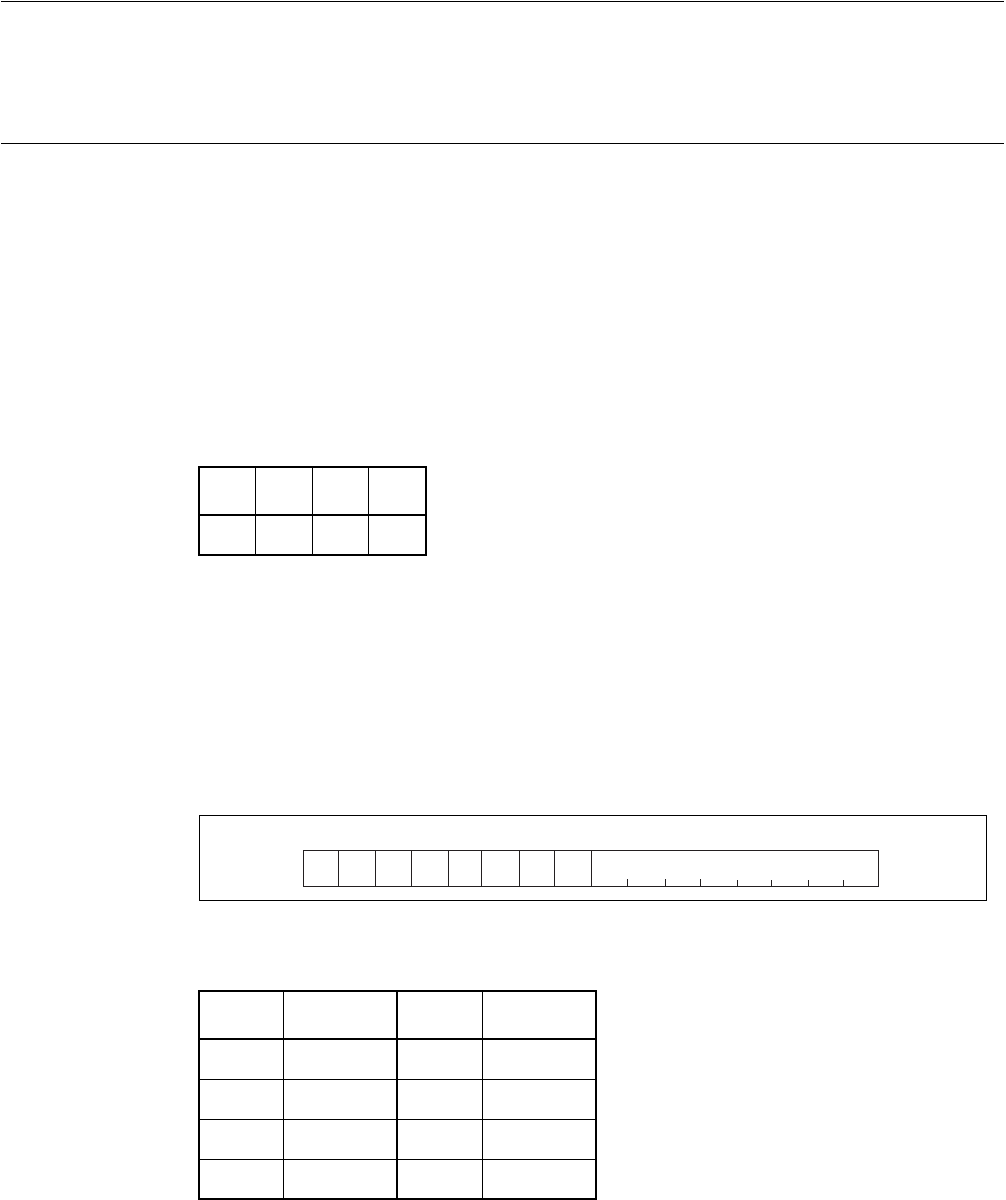

Instruction format:

NZVC

––––

Table 7.131-1 Bit Values and Register Numbers for "reglist" (STM0)

Bit Register Bit Register

7R03R4

6R12R5

5R21R6

4R30R7

MSB LSB

10001110

reglist